## Power Quality and Efficiency Improvements for Transformerless Grid Connected PV Inverters

by

Leslie Alan Bowtell, MEng, BEng, RPEQ

#### Dissertation

Submitted in Fulfilment of the requirements for the degree of Doctor of Philosophy at the

### University of Southern Queensland

Faculty of Engineering and Surveying November 2010

## Abstract

There is currently significant growth in the number of residential scale gridconnected photovoltaic (PV) systems. Generally, if environmental costs are not accounted for, the cost of generation from PV sources remains high compared to conventionally generated electricity. There is, therefore, a strong incentive to reduce the cost of PV systems and improve their efficiency while satisfying injected power quality standards. The focus has been on the power electronic single phase converter bridge which is typically used as interface between the DC output of the PV panels and the terminals of the AC network. One of the two main objectives was to investigate the possibility of operating an inverter connected to the AC grid without an interfacing power transformer, while keeping DC injection into the grid below levels specified by Australian and International Standards. A low cost method of controlling the DC offset content of the current injected into the AC mains has been proposed. A mathematical model of the DC offset controller has been developed and experimentally validated. A design procedure for the controller has also been developed. The second objective was to investigate the dependence of efficiency on inverter switching strategies such as bipolar and unipolar switching. It was confirmed by specially designed tests that unipolar switching meant significantly lower switching losses when compared with bipolar switching. However, the quality of current injected into the AC mains in the case of unipolar switching was not considered acceptable because of significant current distortion near the AC mains voltage zero crossing. A new method of inverter switching has been proposed which exploits the efficiency advantage of unipolar switching while avoiding the problem of current distortion. The main outcomes of this project are a DC offset controller which allow transformerless operation and an inverter switching strategy that results in significantly reduced switching losses while maintaining the quality of injected current. Implementation of the proposed DC offset controller and inverter switching strategy will result in both capital cost savings and higher conversion efficiency.

# **Certification of Thesis**

I certify that the ideas, experimental work, results, analyses, software and conclusions reported in this dissertation are entirely my own effort, except where otherwise acknowledged. I also certify that the work is original and has not been previously submitted for any other award, except where otherwise acknowledged.

Signature of Candidate

ENDORSEMENT

Signature of Supervisor

Signature of Supervisor

Date

Date

Date

## Acknowledgments

I wish to convey my most sincere thanks to my supervisor Dr Tony Ahfock for his help throughout this project. He has provided excellent supervision, skilful guidance and tactful mentoring from the inception of this project right through to the compilation of this thesis. He has made this a rewarding although sometimes challenging experience for which I am sincerely grateful to have had such a gifted and fervent mentor.

I wish also to thank USQ's technical staff, in particular Mr Don Gelhaar for his assistance in the Laboratory, and for his kind words of encouragement.

It also goes without saying that without the continuous support and motivation received from my family, particularly my wife Shelley, that this dissertation would not have been possible. Lastly but certainly not least I wish to thank my three children for the tolerance and patience that they have shown me over the last three years and for foregoing all the weekend activities for which I am now once again available.

## Contents

| Abst   | ract     |                                                | i    |  |

|--------|----------|------------------------------------------------|------|--|

| Certi  | fication | n of Thesis                                    | ii   |  |

| Ackr   | nowledg  | gements                                        | iii  |  |

| Cont   | ents     |                                                | iv   |  |

| List o | of Table | es                                             | ix   |  |

| List o | of Figur | res                                            | Х    |  |

| List o | of Symł  | bols                                           | xiii |  |

| Publi  | ications |                                                | XV   |  |

| 1      | Intro    | oduction                                       |      |  |

|        | 1.1      | Justification for the Research Project         | 1    |  |

|        | 1.2      | Aims and objectives                            | 3    |  |

|        | 1.3      | Outline of Dissertation                        | 4    |  |

|        | 1.4      | Summary of Outcomes                            | 5    |  |

| 2      | Con      | Common Inverter Control Strategies             |      |  |

|        | 2.1      | Inverter Control Strategies                    | 6    |  |

|        | 2.2      | Voltage versus Current Control                 | 6    |  |

|        | 2.3      | Inverter Switching Methodologies               | 9    |  |

|        |          | 2.3.1 Bipolar Switching                        | 10   |  |

|        |          | 2.3.2 Unipolar Switching                       | 11   |  |

|        | 2.4      | System Control Loops                           | 12   |  |

|        |          | 2.4.1 DC Bus Voltage Control                   | 13   |  |

|        |          | 2.4.2 Maximum Power Tracker                    | 15   |  |

|        | 2.5      | Potential for Cost and Performance improvement | 19   |  |

| 3 | Literatu | re Review and Project Plan                                | 20 |

|---|----------|-----------------------------------------------------------|----|

|   | 3.1 I    | Review of Literature                                      | 20 |

|   |          | 3.1.1 DC Offset Control                                   | 20 |

|   |          | 3.1.2 Output Current Harmonic Distortion                  | 24 |

|   | 3.2      | Project Plan                                              | 28 |

| 4 | Selectio | on of Inverter Topology                                   |    |

|   | 4.1      | Comparison of Bipolar and Unipolar Control                | 29 |

|   | 4.2      | Bipolar Switching without Ripple Filter                   | 31 |

|   | 4.3      | The Ripple Filter                                         | 34 |

|   | 4.4      | Filter Damping                                            | 38 |

|   | 4.5      | Bipolar Switching with Ripple Filter                      | 43 |

|   | 4.6      | Expected Switching Loss Reduction with Unipolar Switching | 46 |

|   | 4.7      | Unipolar Switching without Ripple Filter                  | 48 |

|   | 4.8      | Unipolar Switching with Ripple Filter                     | 51 |

|   | 4.9      | Mixed Bipolar and Unipolar Switching                      | 53 |

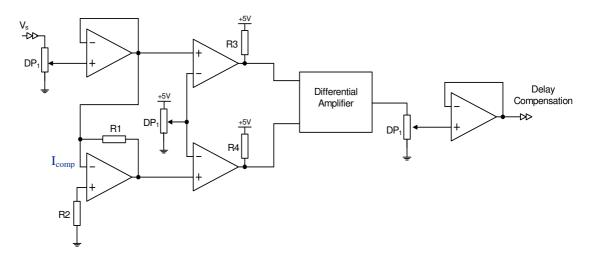

|   | 4.10     | The Effect of Delay                                       | 57 |

|   | 4.11     | The Effect of Delay on Bipolar Switching                  | 60 |

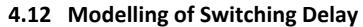

|   | 4.12     | Modelling of Switching Delay                              | 61 |

|   | 4.13     | Compensation for the Effect of Delay                      | 63 |

|   | 4.14     | Thermal Tests                                             | 66 |

|   | 4.15     | Summary                                                   | 68 |

|   |          |                                                           |    |

| 5 | DC  | Bus Voltage Controller                            |     |

|---|-----|---------------------------------------------------|-----|

|   | 5.1 | Introduction                                      | 69  |

|   | 5.2 | Maximum Power tracker                             | 71  |

|   | 5.3 | DC Bus Voltage Controller                         | 73  |

|   | 5.4 | Dynamic Analysis of the DC Bus Voltage Controller | 76  |

| 6 | DC  | Offset Control                                    |     |

|   | 6.1 | Introduction                                      | 79  |

|   | 6.2 | RLLC Sensor Based DC Offset Controller            | 80  |

|   |     | 6.2.1 Mathematical Model                          | 81  |

|   |     | 6.2.2 Controller Design                           | 85  |

|   |     | 6.2.3 Test Results                                | 87  |

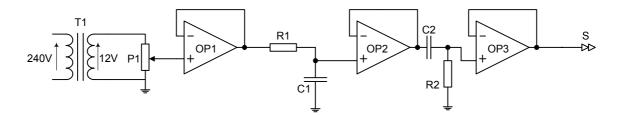

|   | 6.3 | Dual-Stage RC Sensor Based DC Offset Controller   | 90  |

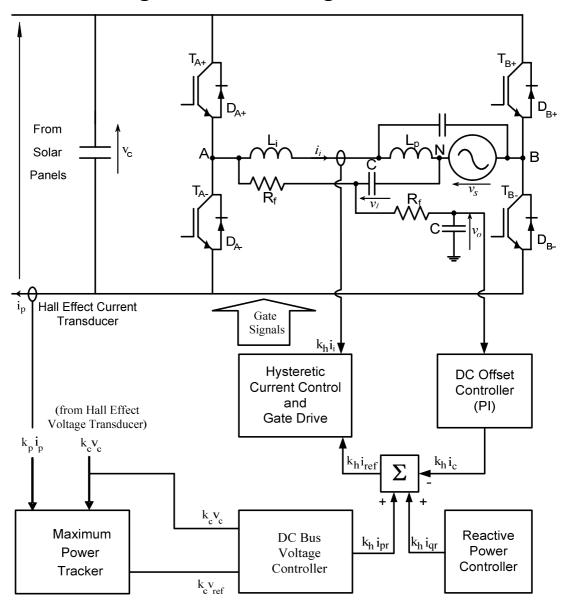

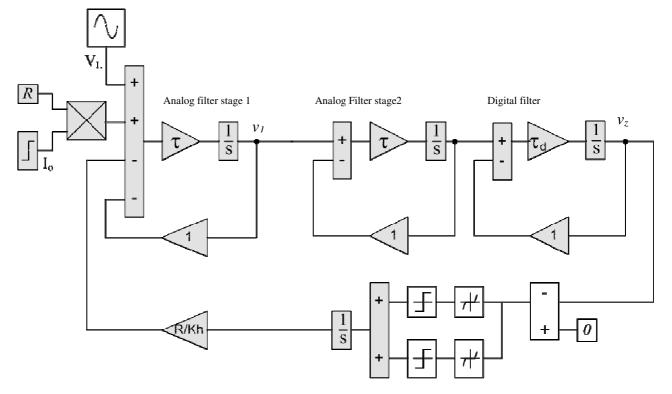

|   |     | 6.3.1 Mathematical model                          | 91  |

|   |     | 6.3.2 Controller design                           | 94  |

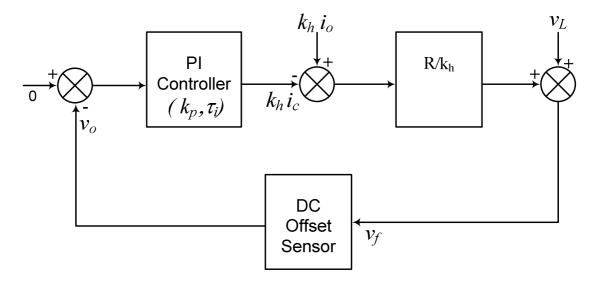

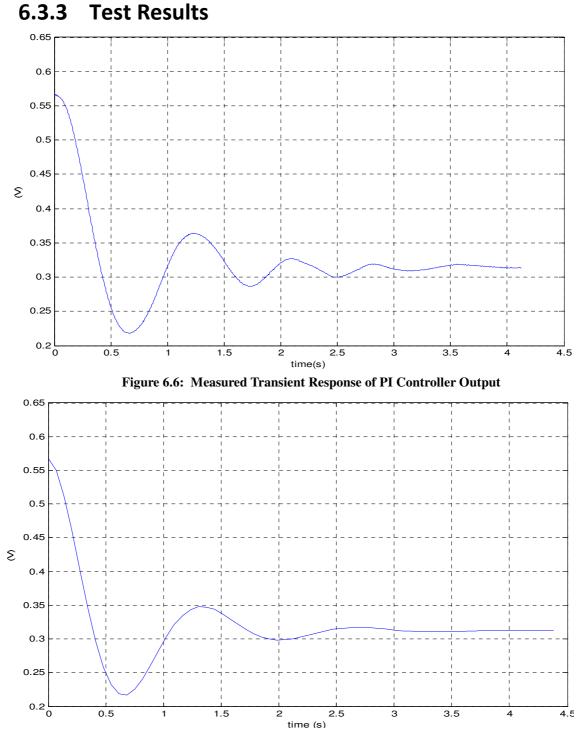

|   |     | 6.3.3 Test Results                                | 98  |

|   | 6.4 | Dual-Stage RC Based Digital DC Offset Controller  | 100 |

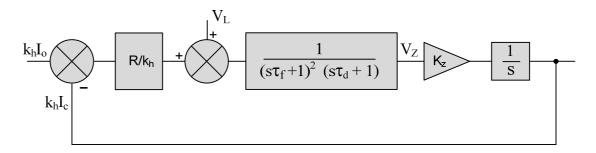

|   |     | 6.4.1 Mathematical Model                          | 103 |

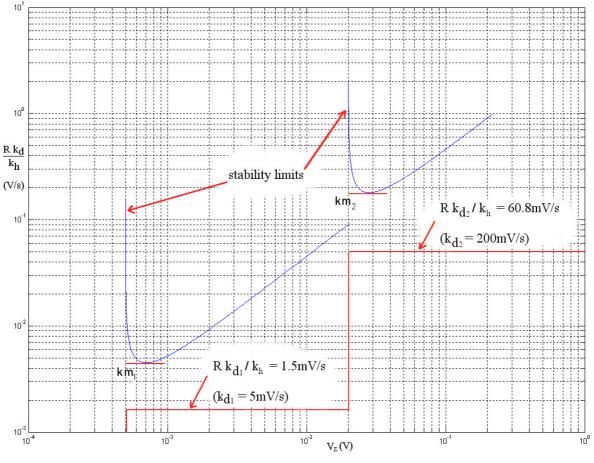

|   |     | 6.4.2 Controller Design                           | 104 |

|   |     | 6.4.3 Test Results                                | 108 |

|   | 6.5 | DC Offset and Bus Voltage Controller Interaction  | 111 |

### 7. Conclusions

| 7.1 | DC Offset Control               | 116 |

|-----|---------------------------------|-----|

| 7.2 | Reduction in Current Distortion | 117 |

| 7.3 | Summary                         | 120 |

|     |                                 |     |

### 8. References

### Appendix A

126

121

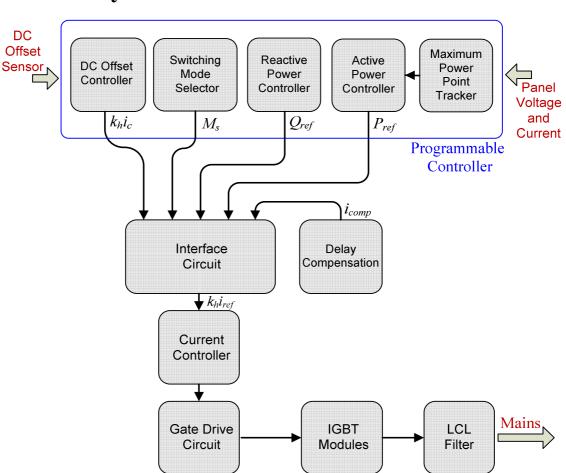

| A.1:  | System Overview                                           | 127 |

|-------|-----------------------------------------------------------|-----|

| A.2:  | Illustration of Inverter Non-Unity Power Factor Operation | 129 |

| A.3:  | Zero Phase-Shift Filter                                   | 130 |

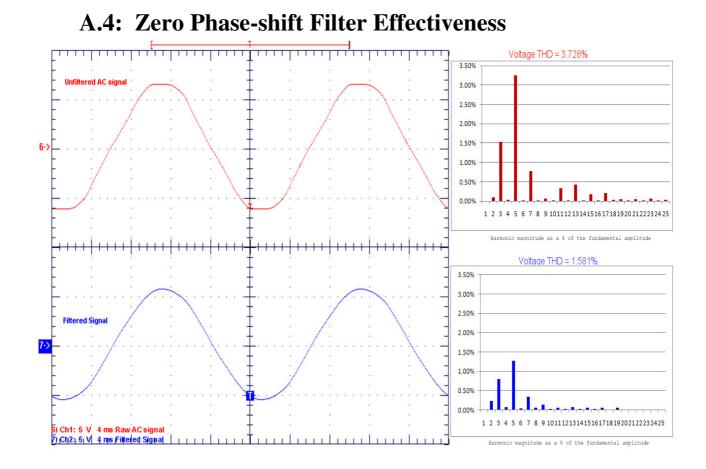

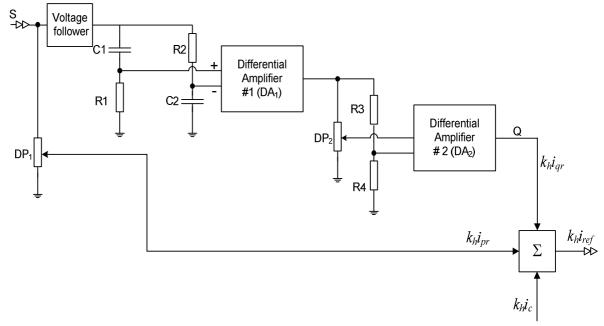

| A.4:  | Effectiveness of Zero Phase-Shift Filter                  | 131 |

| A.5:  | Active and Reactive Components of $k_h i_{ref}$           | 132 |

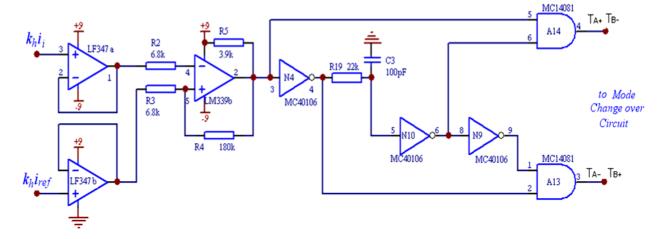

| A.6:  | Bipolar Current Controller                                | 133 |

| A.7:  | Unipolar Current Controller                               | 134 |

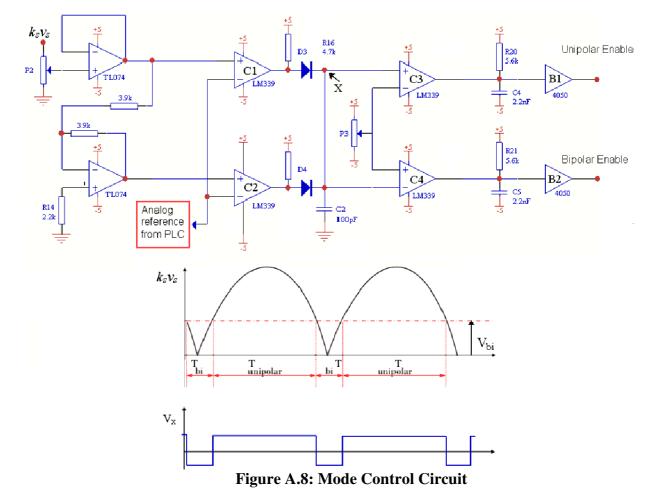

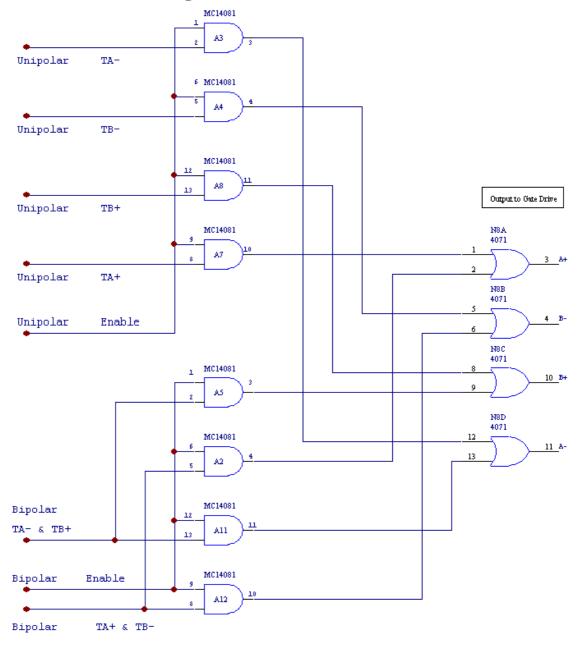

| A.8:  | Multi-Mode Controller Schematic                           | 135 |

| A.9:  | Mode Change-Over Circuit                                  | 137 |

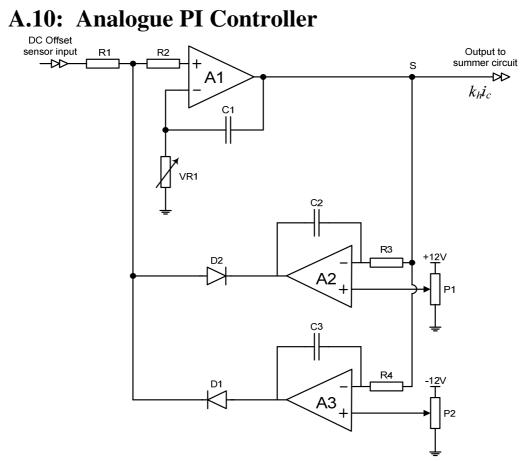

| A.10: | Analogue PI Controller                                    | 138 |

|       |                                                           |     |

| Appendix B |                 |     |

|------------|-----------------|-----|

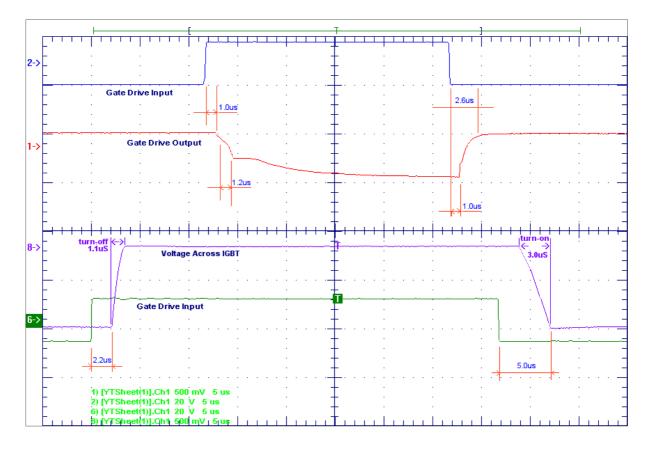

| B.1:       | Switching Delay | 139 |

# **List of Tables**

| Table 4.1: | Filter Power Loss Comparison                         | 41  |

|------------|------------------------------------------------------|-----|

| Table 4.2: | Unipolar Switching Logic                             | 49  |

| Table 4.3: | Multi-mode Switching Logic                           | 54  |

| Table 4.4: | Thermal Rise Temperature Tests                       | 67  |

| Table 6.1: | DC Offset Controller Design Parameters               | 97  |

| Table 6.2: | DC Offset Currents at Various Inverter Output Levels | 114 |

# **List of Figures**

| Figure 1.1:    | Essential Components of a Grid-Connected Photovoltaic System       | 1  |

|----------------|--------------------------------------------------------------------|----|

| Figure 2.1:    | Output Voltage from Unipolar Switched Inverter                     | 7  |

| Figure 2.2:    | Output Voltage from Bipolar Switched Inverter                      | 7  |

| Figure 2.3:    | Typical Unfiltered Output Current of a Current Controlled Inverter | 8  |

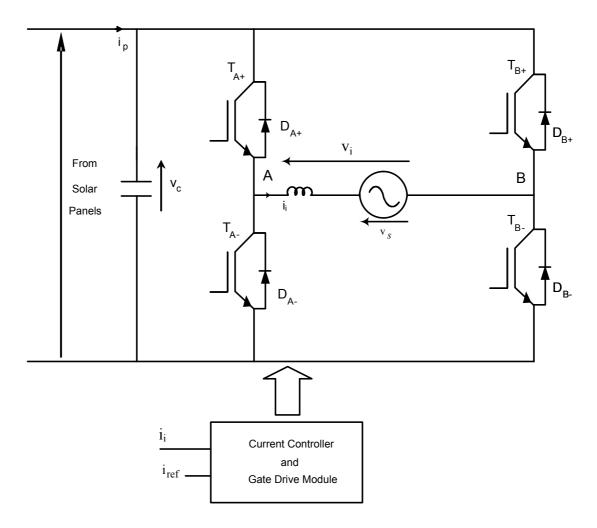

| Figure 2.4:    | Current Controlled Grid Connected Full Bridge Inverter             | 9  |

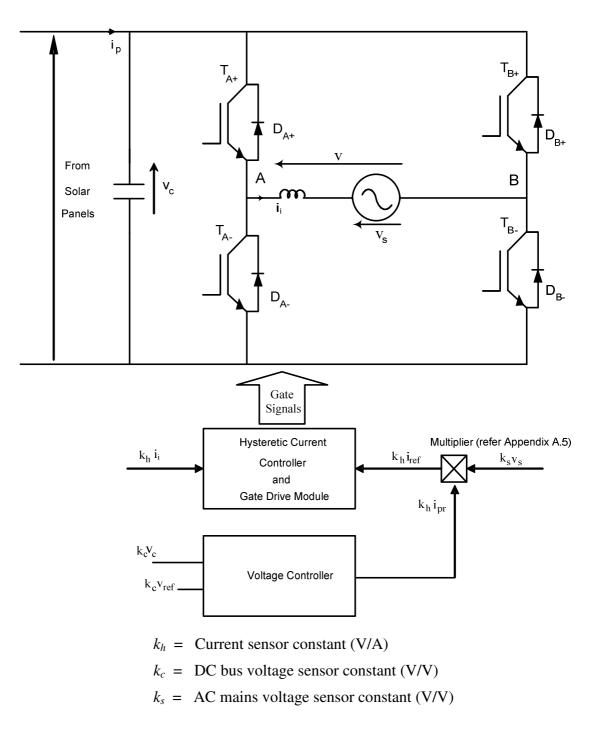

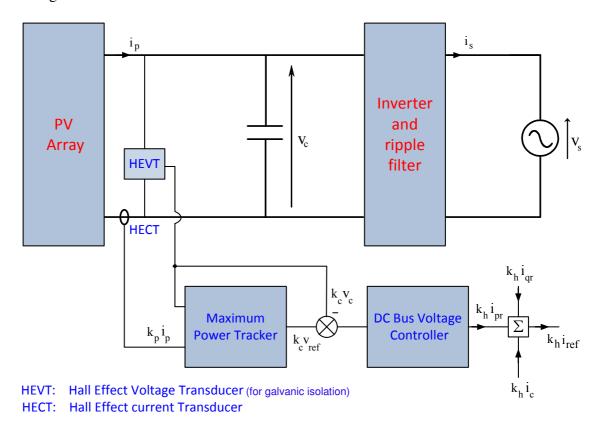

| Figure 2.5:    | Inverter and Bus Voltage Control Loop                              | 14 |

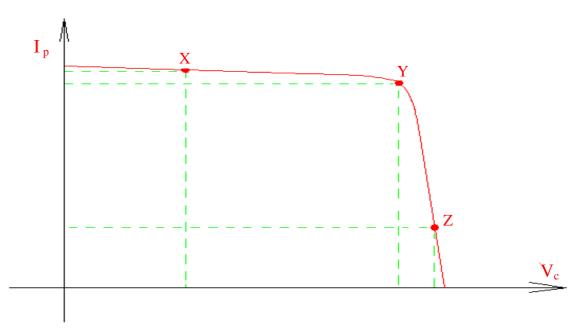

| Figure 2.6:    | PV Array Characteristic at Given Insolation and Temperature        | 15 |

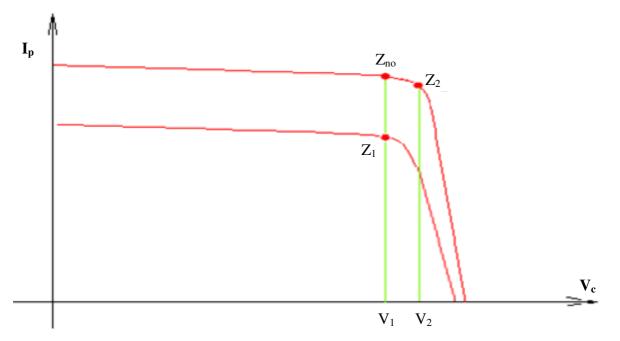

| Figure 2.7:    | The Need for Maximum Power Tracking                                | 16 |

| Figure 2.8:    | Grid Connected PV System with Maximum Power Tracker                | 17 |

| Figure 4.1:    | Inverter Components including LCL filter                           | 30 |

| Figure 4.2:    | Simplified Bipolar Inverter Control model                          | 31 |

| Figure 4.3:    | Hysteretic control (no ripple filter)                              | 32 |

| Figure 4.4:    | Simplified bipolar inverter circuit                                | 32 |

| Figure 4.5:    | Theoretical Bipolar operation 2.0A                                 | 33 |

| Figure 4.6:    | Experimental Bipolar operation 2.0A                                | 33 |

| Figure 4.7:    | LCL Filter Components                                              | 34 |

| Figure 4.8:    | Undamped filtered waveform                                         | 38 |

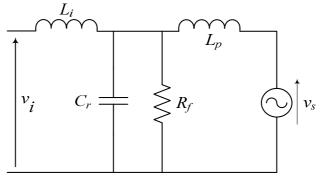

| Figure 4.9:    | Filter Damping Options                                             | 39 |

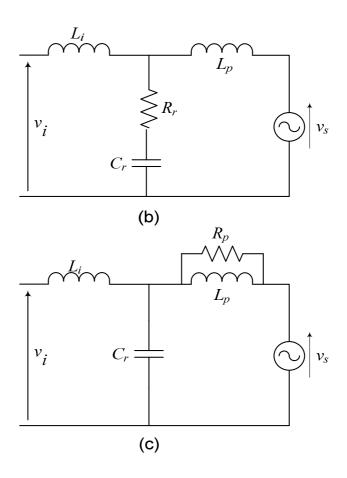

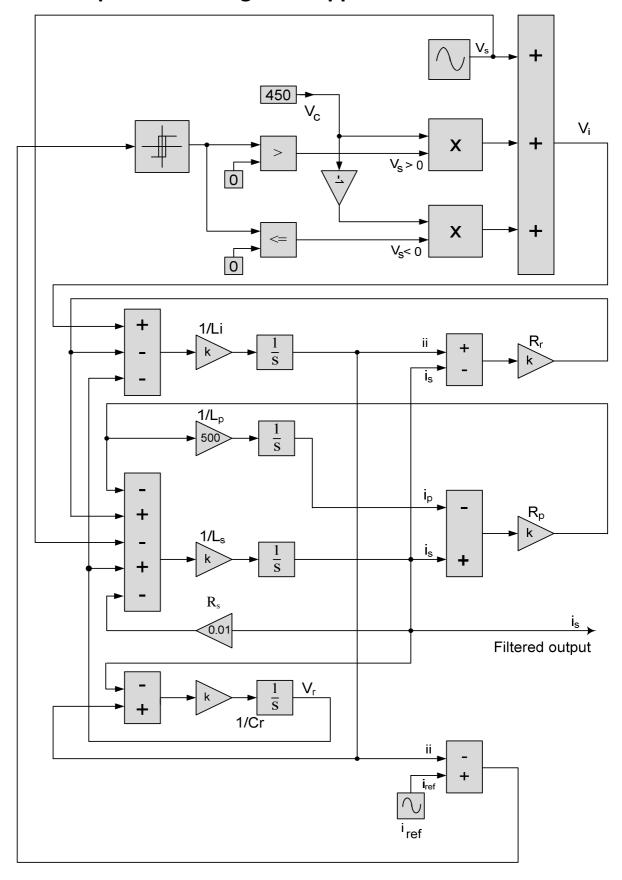

| Figure 4.10:   | Simulink Model of the LCL Filter                                   | 43 |

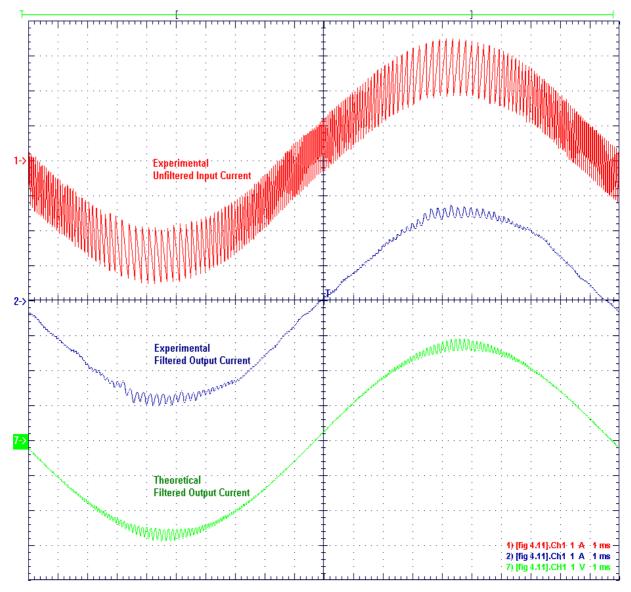

| Figure 4.11:   | Theoretical and Experimental LCL Filter Effect                     | 44 |

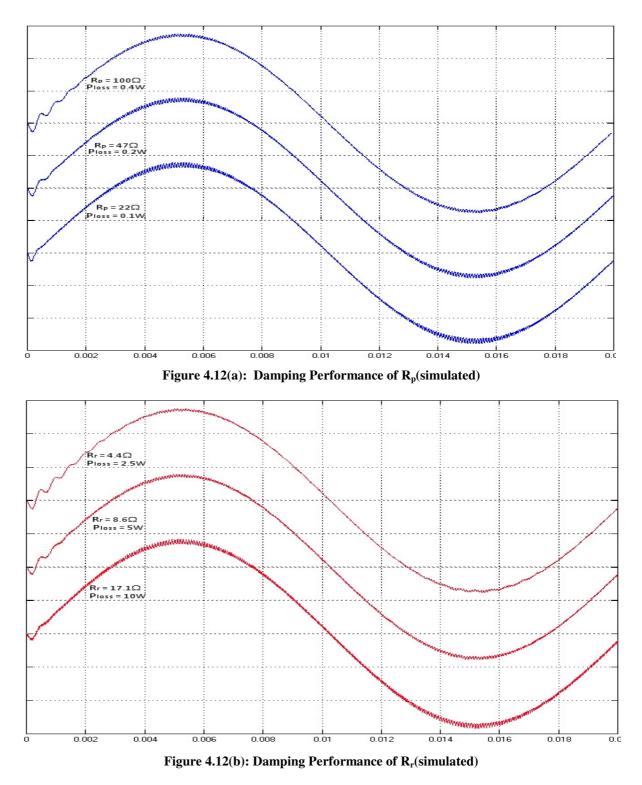

| Figure 4.12(a) | : Damping Performance of $R_p$ (simulated)                         | 45 |

| Figure 4.12(b) | : Damping Performance of $R_r$ (simulated)                         | 45 |

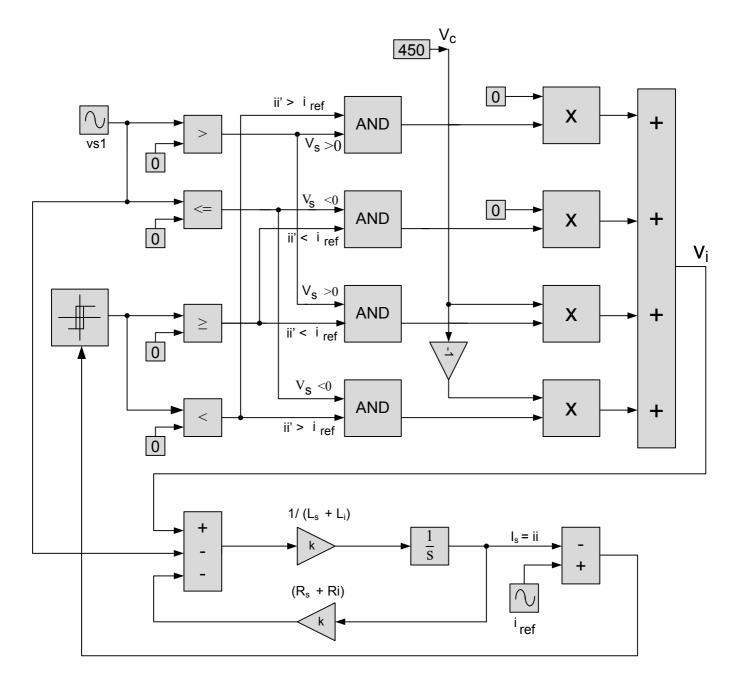

| Figure 4.13:   | Unipolar Switched Inverter Model                                   | 48 |

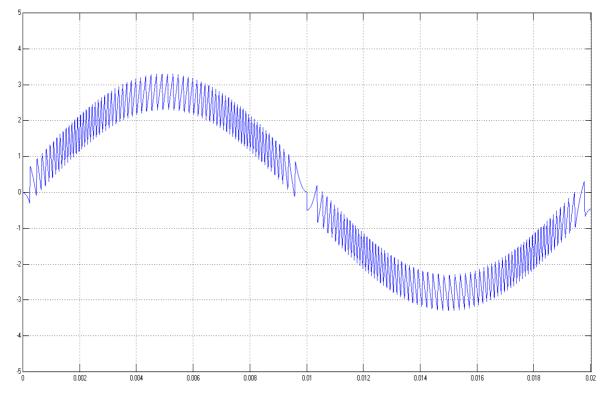

| Figure 4.14: | Theoretical Unfiltered Unipolar Operation 2A (no delay)     | 49 |

|--------------|-------------------------------------------------------------|----|

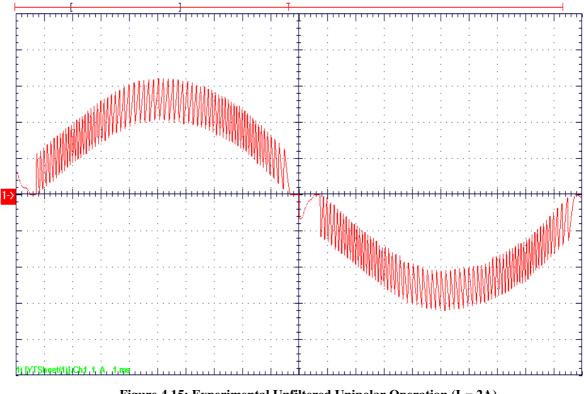

| Figure 4.15: | Experimental Unfiltered Unipolar Operation 2A               | 50 |

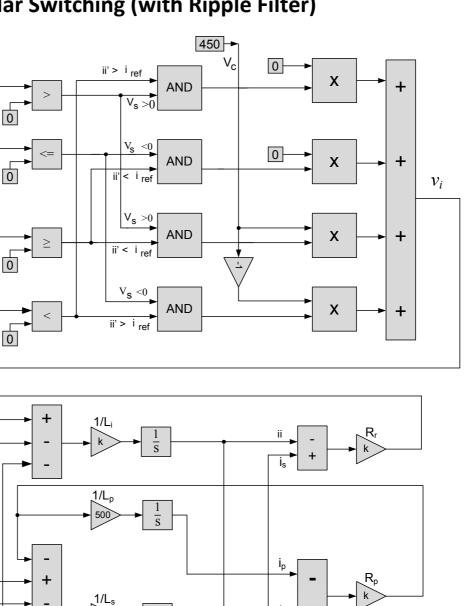

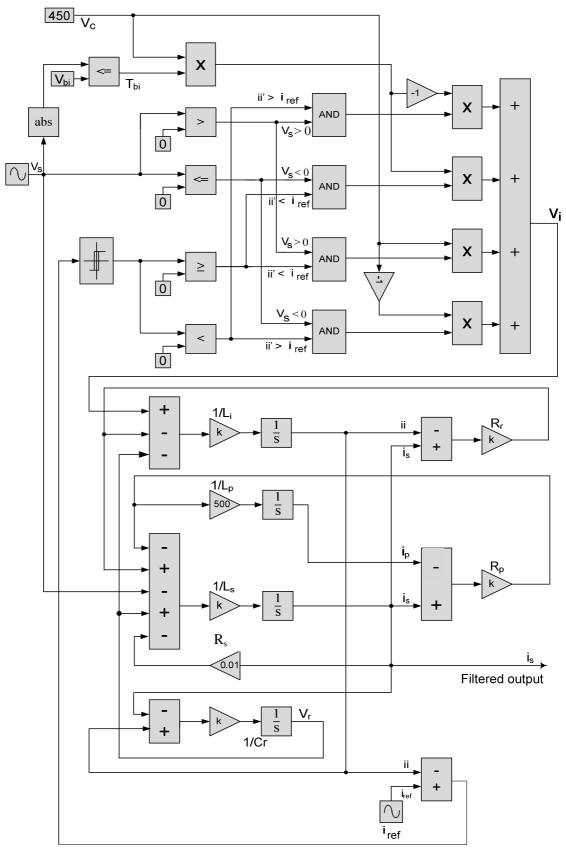

| Figure 4.16: | Unipolar Switched Inverter Model                            | 51 |

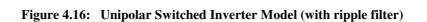

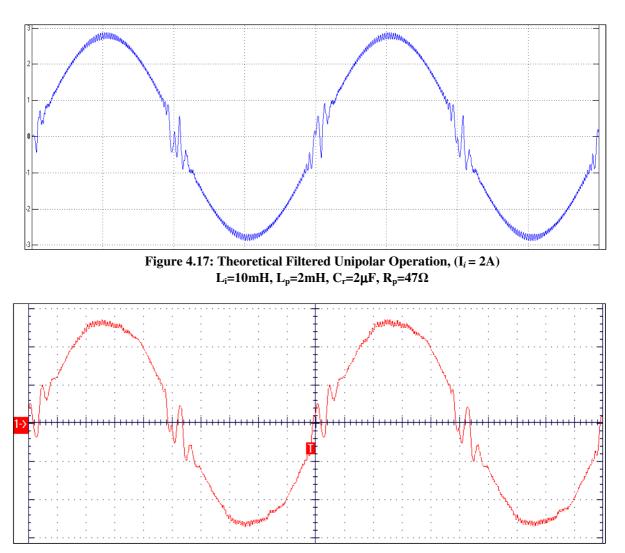

| Figure 4.17: | Theoretical Filtered Unipolar Operation 2A                  | 52 |

| Figure 4.18: | Experimental Filtered Unipolar Operation 2A                 | 52 |

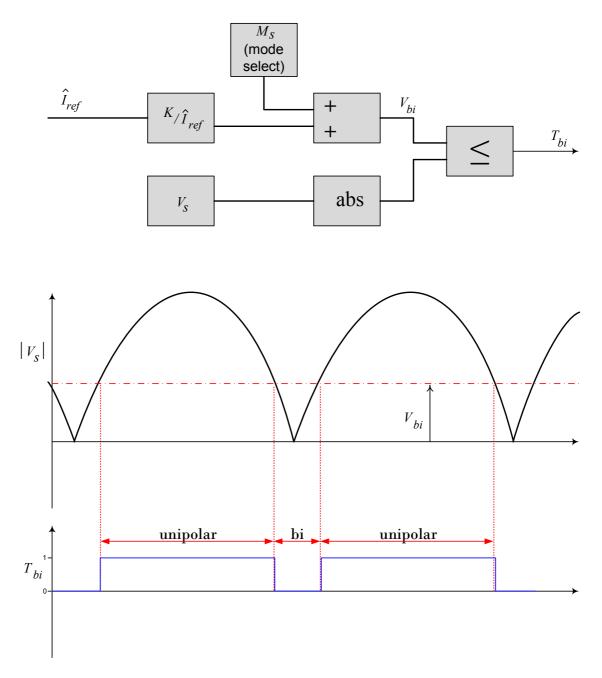

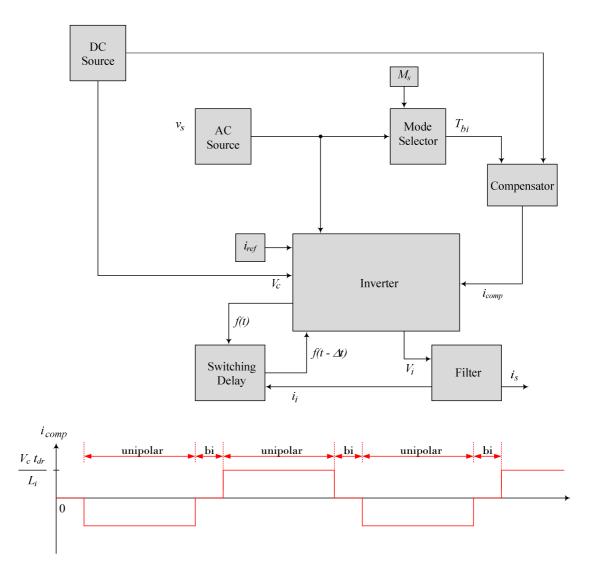

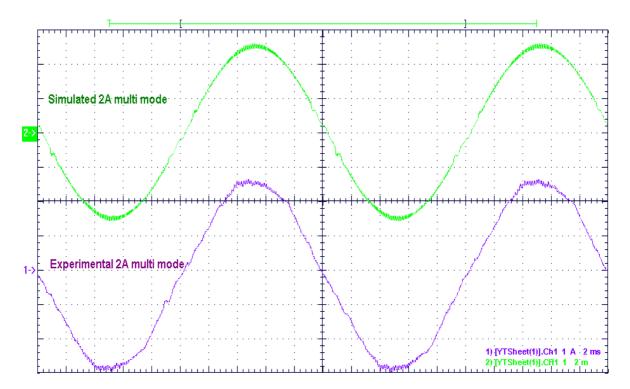

| Figure 4.19: | Mixed-mode Inverter Block Diagram                           | 53 |

| Figure 4.20: | Mixed-mode Selector Block diagram                           | 55 |

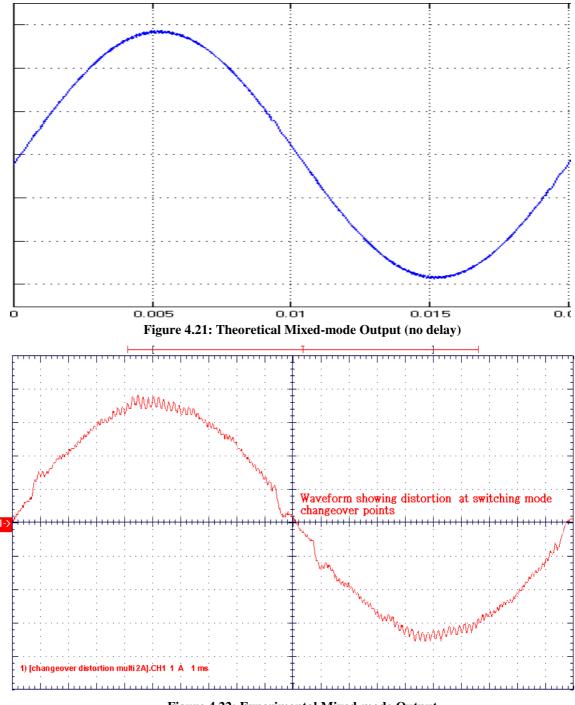

| Figure 4.21: | Theoretical Mixed-mode Output (no delay)                    | 56 |

| Figure 4.22: | Experimental Mixed-mode Output                              | 56 |

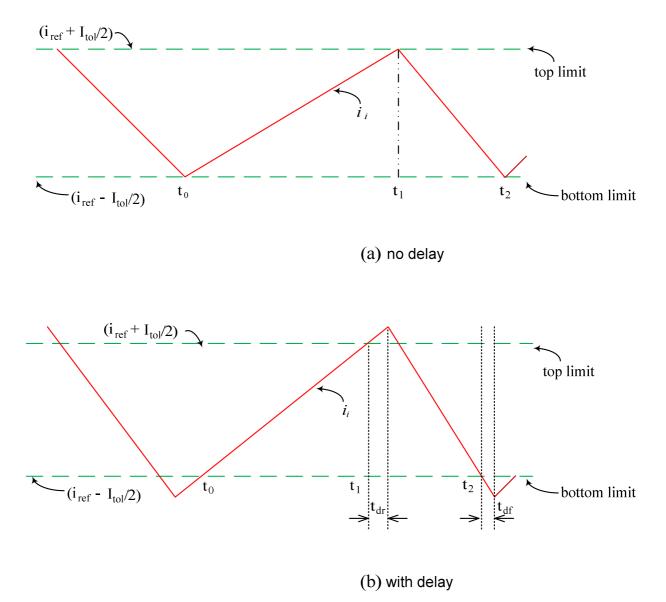

| Figure 4.23: | Effects of Switching Delay                                  | 57 |

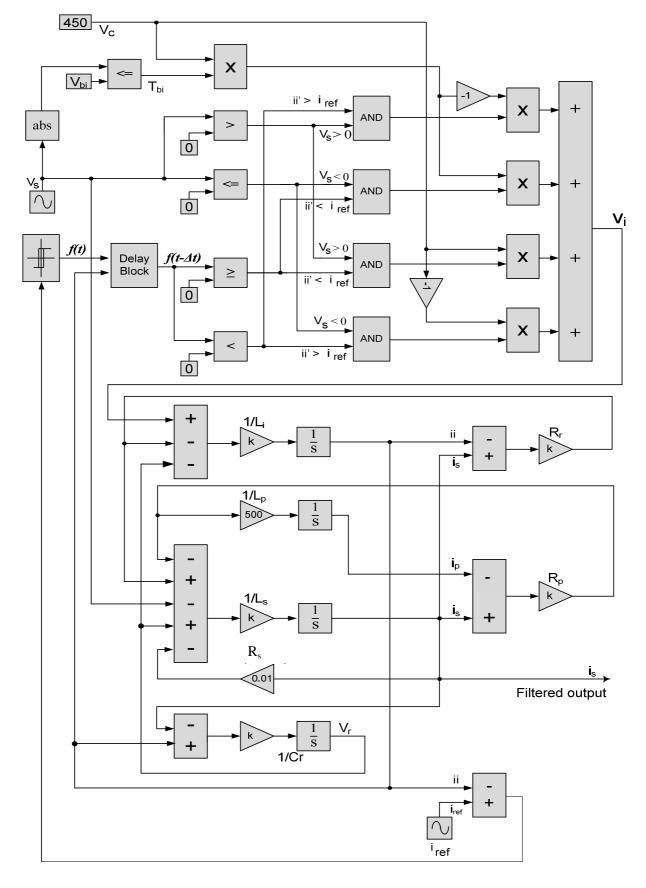

| Figure 4.24: | Mixed-mode Inverter Model with Switching Delay included     | 61 |

| Figure 4.25: | Simulink® Block Representing Switching Delay in figure 4.24 | 62 |

| Figure 4.26: | Simulated Mixed-mode Operation with Switching Delay of 5µs  | 63 |

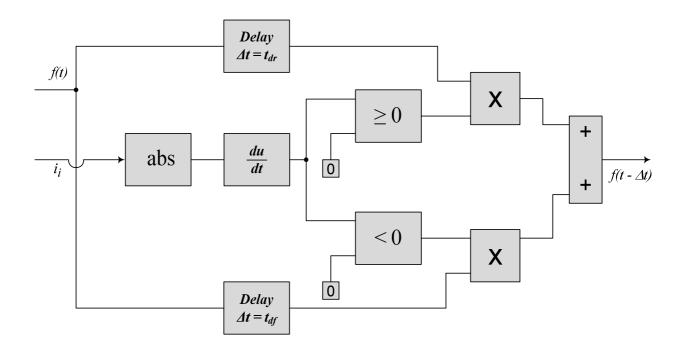

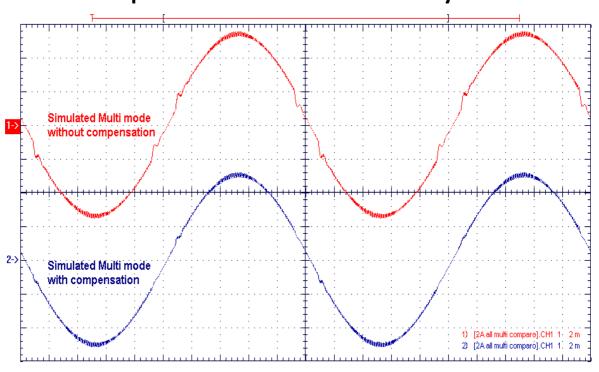

| Figure 4.27: | Harmonic Content Comparison with and without Compensation   | 63 |

| Figure 4.28: | Mixed-mode Inverter Block Diagram with Delay & Compensation | 64 |

| Figure 4.29: | Simulated and Experimental Mixed-mode 2A Operation with     |    |

|              | Delay and Compensation                                      | 65 |

| Figure 5.1:  | PV System Components                                        | 69 |

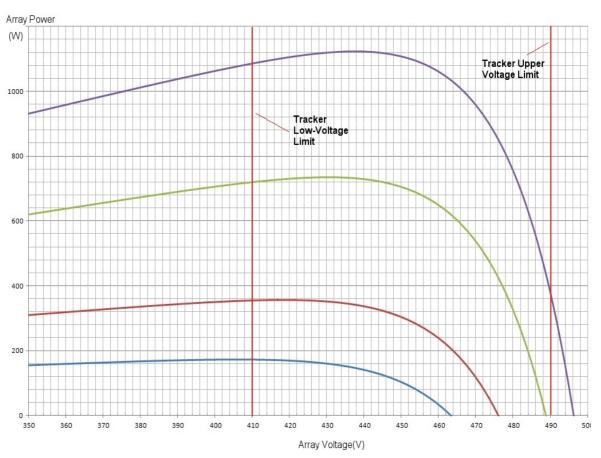

| Figure 5.2:  | PV Array Power versus Insolation Level Curves               | 71 |

| Figure 5.3:  | PV Array Maximum Power tracker                              | 72 |

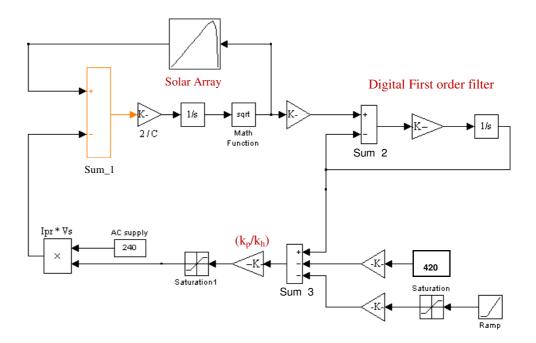

| Figure 5.4:  | DC Bus Voltage Controller Simulink® model                   | 73 |

| Figure 5.5:  | DC Bus Voltage Controller                                   | 75 |

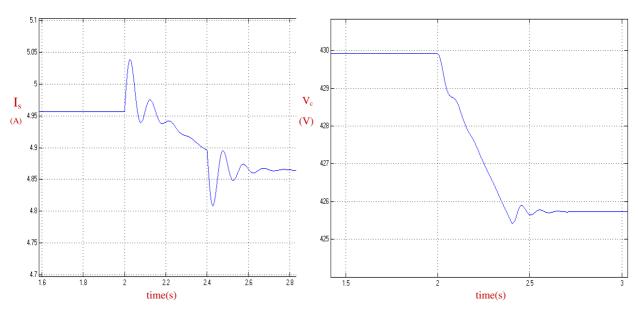

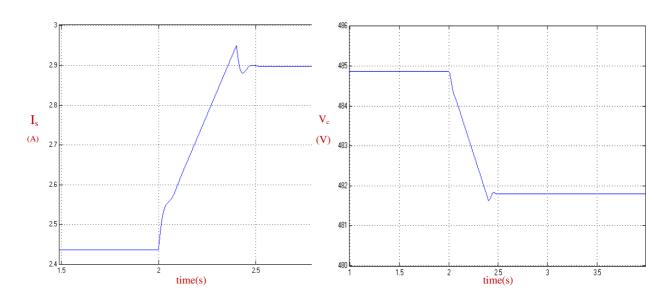

| Figure 5.6:  | DC Bus Voltage Response from 420V to 416V Reference Step    | 78 |

| Figure 5.7:  | DC Bus Voltage Response from 480V to 476V Reference Step    | 78 |

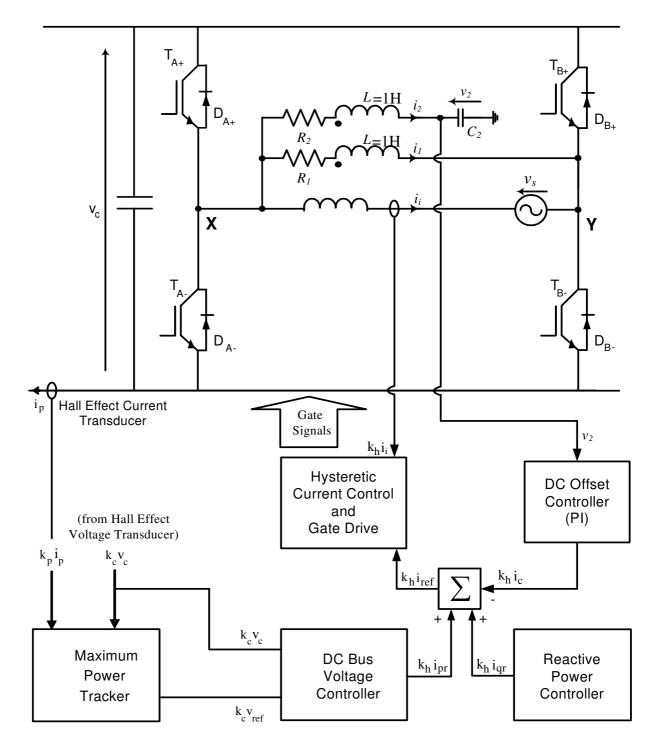

| Figure 6.1:  | RLLC DC Offset System Overview                              | 80  |

|--------------|-------------------------------------------------------------|-----|

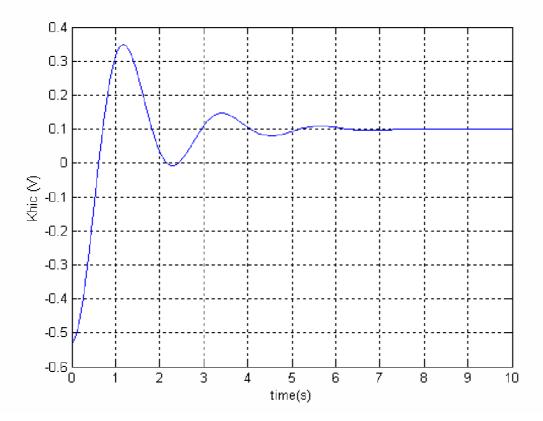

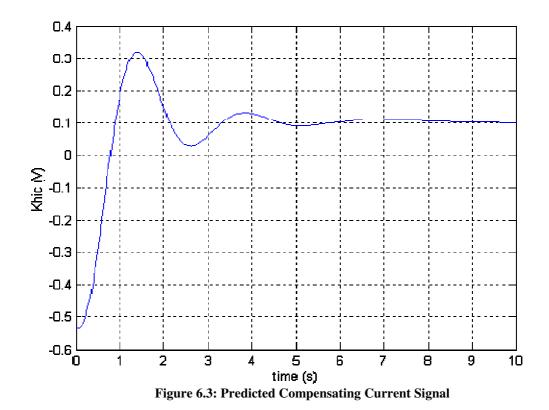

| Figure 6.2:  | Measured Compensating Current Signal                        | 87  |

| Figure 6.3:  | Predicted Compensating Current Signal                       | 87  |

| Figure 6.4:  | Dual-Stage RC Analogue DC Offset Controller System Overview | 90  |

| Figure 6.5:  | DC Offset Sensor Block Diagram                              | 91  |

| Figure 6.6:  | Measured Transient Response of PI Controller Output         | 98  |

| Figure 6.7:  | Simulated Transient Response of PI Controller Output        | 98  |

| Figure 6.8:  | Dual-Stage RC Digital DC Offset Controller System Overview  | 100 |

| Figure 6.9:  | Digital DC Offset Controller Simulink model                 | 103 |

| Figure 6.10: | Controller Block Diagram                                    | 104 |

| Figure 6.11: | Integrator Gain Characteristic                              | 106 |

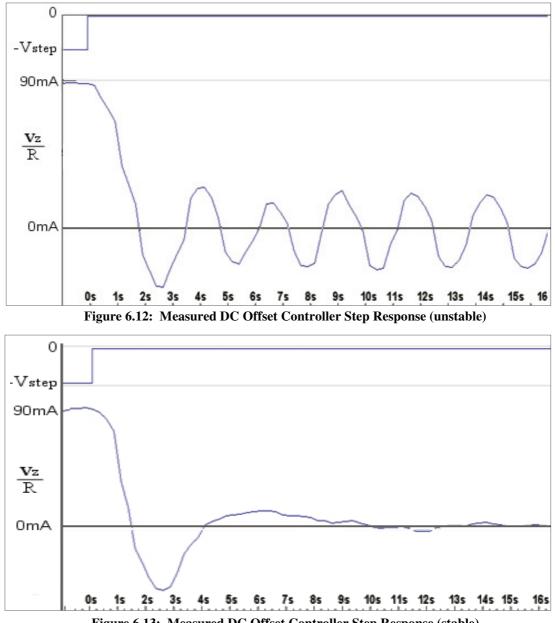

| Figure 6.12: | Measured DC Offset Controller Step Response (unstable)      | 108 |

| Figure 6.13: | Measured DC Offset Controller Step Response (stable)        | 108 |

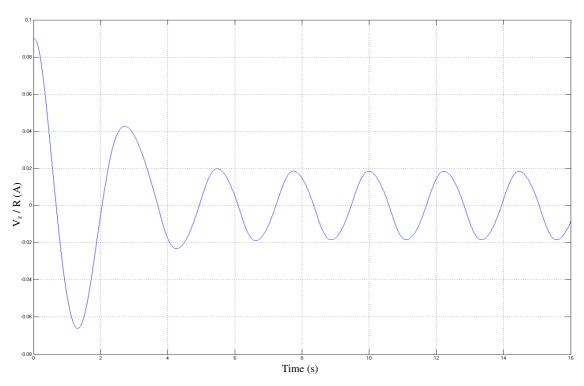

| Figure 6.14: | Simulated DC Offset Controller Step Response (stable)       | 109 |

| Figure 6.15: | Simulated DC Offset Controller Step Response (stable)       | 109 |

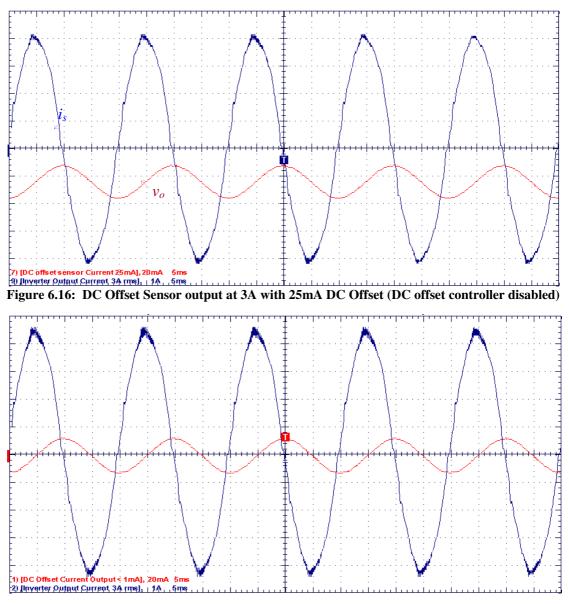

| Figure 6.16: | DC Offset Sensor output at 3A with 25mA DC Offset           | 110 |

| Figure 6.17: | DC Offset Sensor output at 3A with <1mA DC Offset           | 110 |

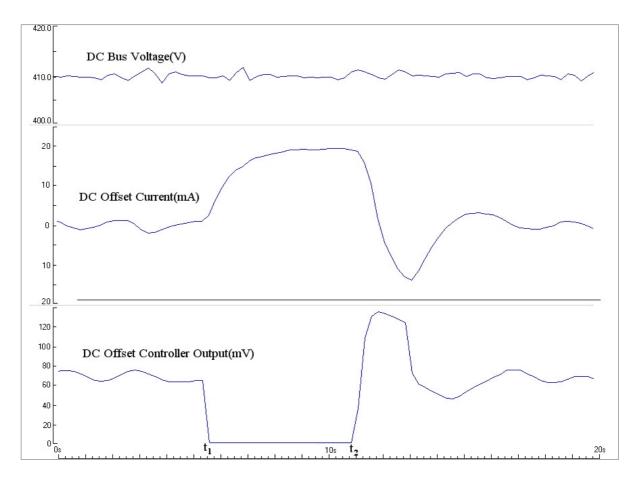

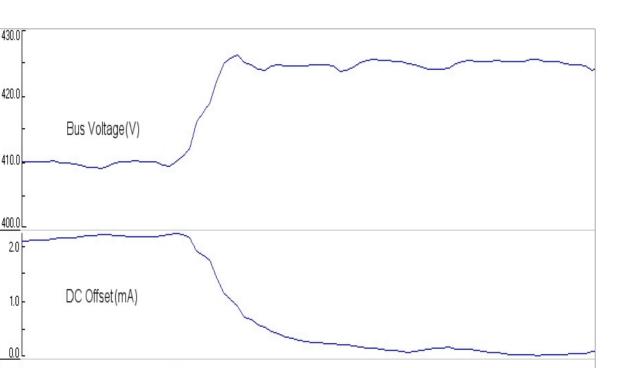

| Figure 6.18: | Non-Interaction between DC Offset and DC Bus Control Loops  | 112 |

| Figure 6.19: | Apparent coupling between Bus Voltage and DC Offset Loops   | 113 |

# **List of Symbols**

| $i_i$                  | inverter output current                                                                      |

|------------------------|----------------------------------------------------------------------------------------------|

| $i_c$                  | DC offset correction current (output of the DC offset controller)                            |

| $i_{comp}$             | component of $i_{ref}$ to compensate for switching delay(see figure 4.28)                    |

| $i_o$                  | inherent DC offset content of the inverter output                                            |

| $i_p$                  | output current from PV array                                                                 |

| $i_{pr}$               | active power component of current reference                                                  |

| $i_{qr}$               | reactive power component of current reference                                                |

| <i>i<sub>ref</sub></i> | current reference to hysteretic current controller                                           |

| $i_s$                  | AC mains or grid supply current                                                              |

| <i>k</i> <sub>c</sub>  | DC bus voltage sensor constant (V/V)                                                         |

| <i>k</i> <sub>e</sub>  | proportional gain of analogue PI controller                                                  |

| $k_h$                  | Hall effect current sensor constant (V/A)                                                    |

| $k_m$                  | coupling factor of 1:1 inductor pair (see figure 6.2)                                        |

| $k_p$                  | Hall effect current sensor on DC side(V/A)                                                   |

| $k_s$                  | AC mains voltage sensor constant (V/V)                                                       |

| $k_z v_z$              | = $k_{d1}$ or $k_{d2}$ = constant integration rate of the integral element of the digital DC |

|                        | offset PI controller                                                                         |

| t <sub>dr</sub>        | switching delay on current rise (see figure 4.23)                                            |

| $t_{df}$               | switching delay on current fall (see figure 4.23)                                            |

| $	au_d$                | time constant of first order digital filter used in the digital DC offset sensor             |

| $\tau_{f}$             | RLLC DC offset sensor filter equal to $R_2C_2$ (see figure 6.1)                              |

| $\tau_{f}$             | time constant of each nominally identical stage of the dual RC DC offset sensor              |

| $	au_m$                | time constant of the DC Bus voltage sensor for maximum power tracker                         |

| $	au_i$                | analogue PI controller integration time constant                                             |

| $	au_p$                | L/R ratio of each inductor making up the RLLC DC offset sensor                               |

| $T_{bi}$               | Mixed-mode current controller bipolar operation time                                         |

| $T_{A+}$               | Inverter H-Bridge IGBT, top left (see figure 4.4)                                            |

| $T_{A-}$               | Inverter H-Bridge IGBT, bottom left (see figure 4.4)                                         |

| $T_{B+}$               | Inverter H-Bridge IGBT, top right (see figure 4.4)                                           |

| $T_{B-}$               | Inverter H-Bridge IGBT, bottom right (see figure 4.4)                                        |

| v                     | Inverter output voltage                                                  |

|-----------------------|--------------------------------------------------------------------------|

| $v_f$                 | input voltage across dual stage RC DC offset sensor                      |

| $v_c$                 | PV Array bus voltage                                                     |

| $v_m$                 | digitally filtered PV Array bus voltage for MPPT                         |

| Vi                    | integrator output voltage in analogue PI controller                      |

| $v_L$                 | AC component of $v_f$ (defined above)                                    |

| $V_{O}$               | output voltage of dual stage RC DC offset sensor (see figures 6.4, 6.8)  |

| Vref                  | reference DC bus voltage                                                 |

| Vs                    | Mains or grid supply AC voltage                                          |

| $v_z$                 | output voltage of digital filter in digital DC offset controller         |

| <i>v</i> <sub>1</sub> | output of first stage of dual stage RC DC offset sensor (see figure 6.4) |

|                       |                                                                          |

| $D_{A+}$              | Inverter H-Bridge free-wheeling diode, top left (see figure 4.4)         |

| $D_{A}$ -             | Inverter H-Bridge free-wheeling diode, bottom left (see figure 4.4)      |

| $D_{B+}$              | Inverter H-Bridge free-wheeling diode, top right (see figure 4.4)        |

| $D_{B-}$              | Inverter H-Bridge free-wheeling diode, bottom right (see figure 4.4)     |

### ACRONYMS

| EMC  | Electromagnetic Compatibility                                   |

|------|-----------------------------------------------------------------|

| FFT  | Fast Fourier Transform                                          |

| IGBT | Insulated Gate Bipolar Transistor                               |

| MPPT | Maximum Power Point Tracking                                    |

| PV   | Photo-Voltaic                                                   |

| PWM  | Pulse Width Modulation                                          |

| RLLC | DC offset sensor based on 1:1 coupled inductor (see figure 6.2) |

| RFI  | Radio Frequency Interference                                    |

| THD  | Total Harmonic Distortion                                       |

| UPS  | Uninterruptible Power Supplies                                  |

| VSVC | Voltage sourced voltage controlled inverter                     |

| VSCC | Voltage sourced current controlled inverter                     |

# **Publications**

The following publications are the direct outcomes of this research project:

A.Ahfock and L.Bowtell, "DC Offset Elimination in a Transformerless Single Phase Grid-Connected Photovoltaic System", *Australasian Universities Power Engineering Conference*, 'AUPEC 06', Victoria University, Melbourne, 2006.

L.Bowtell and A.Ahfock, "Comparison Between Unipolar and Bipolar Single Phase Grid-Connected Inverters for PV Applications", *Australasian Universities Power Engineering Conference*, 'AUPEC 07', Curtin University, WA, 2007.

L.Bowtell and A.Ahfock, "Direct Current Offset Controller for Transformerless single-Phase Photovoltaic Grid-connected Inverters", *IET Renewable Power and Generation*, vol. 4, iss. 5, pp. 428-437, 2010.

L.Bowtell and A.Ahfock, "Dynamic Analysis of a DC Offset Controller for Grid-Connected Inverters", *Australasian Universities Power Engineering Conference*, 'AUPEC10', Christchurch, NZ, 2010.

A.Ahfock and L.Bowtell, "Mixed Mode Switching of Single-phase Grid-connected Photovoltaic Inverters", *IET Renewable Power and Generation*, (submitted, Nov 2010).

## **Chapter 1: Introduction**

#### 1. Justification for the Research Project

The possibility of severe climate change caused by fossil fuel consumption and the social consequences of depletion of accessible fossil fuel reserves are now of major concern. As a result, the search for more sustainable energy resources is being intensified. On a national scale, the direct conversion of sunlight into electricity (photovoltaic generation) is a relatively small but growing part of the electrical energy mix. Electrical energy suppliers have to accommodate photovoltaic (PV) system connection to their network.

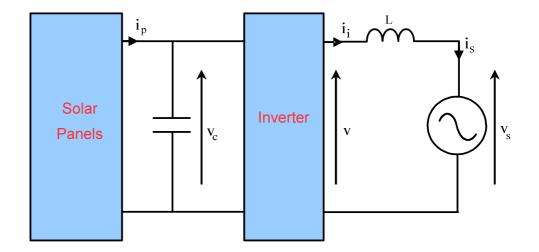

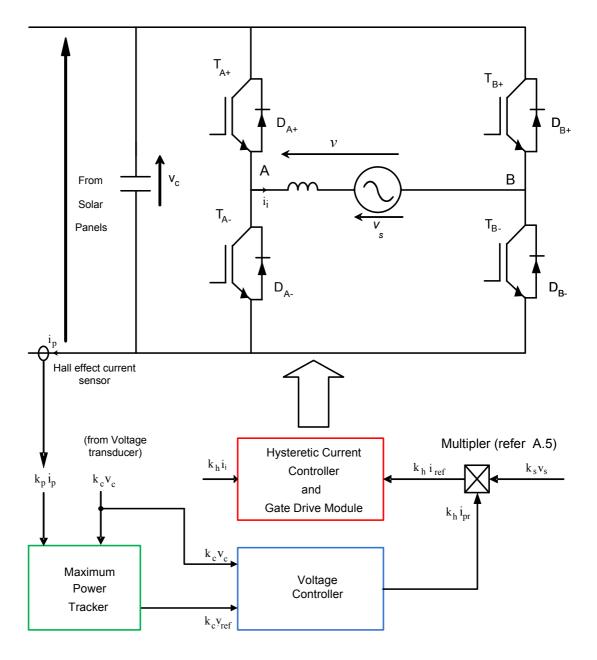

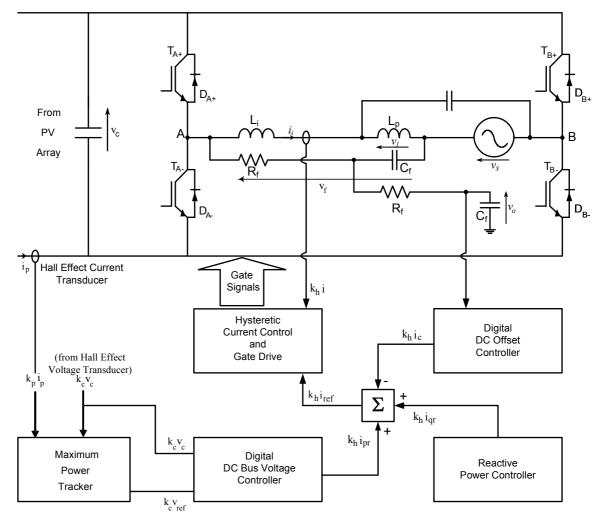

As shown in figure 1.1, a grid connected PV system consists mainly of a set of solar panels and a DC to AC converter. The solar panels convert light energy into direct current (DC). Electrical energy can be fed into the electricity network in alternating (AC) form only. Hence the role of the DC to AC converter (that is, the inverter) is to convert direct current from the solar panels to alternating current (AC) at the standard frequency of 50 Hz before injecting it into the AC network.

Figure 1.1: Essential Components of a Grid-Connected Photovoltaic System

By definition, the highest quality alternating current (AC) would be one which is purely sinusoidal, that is, a current which is a sinusoidal function of time. In practice, however, even the very best inverter will not supply a purely sinusoidal current. The undesirable effects of non-sinusoidal current injection can be serious. For that reason AC network operators impose limits on the degree of distortion away from the ideal sinusoidal current. In particular they specify a limit on the direct current (DC) content of the inverter output, on the lower order harmonic content and on the higher order harmonic content. The low frequency harmonic content typically consists of current components with frequencies equal to multiples of the standard frequency of 50 Hz up to about 1 kHz. Harmonic content at higher frequencies are also present. These are associated with the switching frequencies of devices within the inverter. Limits are also imposed on electromagnetic interference (EMI) caused by fast switching within the inverter.

Apart from the quality of the AC current being injected into the AC network and the level of EMI, two other important factors need to be considered. These are cost and energy conversion efficiency. Cost, conversion efficiency, quality of injected current and the level of EMI generation are not independent factors. For example many suppliers of grid-connected PV systems include a 50 Hz transformer between the output of the inverter and the AC supply so that, among other things, the requirement on DC injection is met. It is well-known that DC current does not flow through a transformer. Thus, while the 50 Hz transformer helps meet injected current quality requirements it adds to system mass, volume, cost and energy losses. Similarly some inverter control or switching strategies lead to better current waveform quality but at the expense of reduced efficiency.

As will be elaborated in the literature review (section 3), very little has been published on DC injection by grid-connected inverters. While feedback control has been suggested for elimination of DC injection, no mathematical models have been proposed for dynamic performance evaluation of DC offset control loops. Similarly, while there are claims that some transformerless inverter switching methods may offer efficiency advantages, to the author's knowledge there is little published physical evidence to support these claims.

#### 1.2 Aim and Objectives

The aim of this work is to select a control and switching strategy for an inverter which is to be used as part of a transformerless single-phase grid-connected PV system, so as to economically achieve better overall efficiency while satisfying operational requirements, in particular those relating to quality of supply.

The objectives are:

- To review different inverter switching strategies and select one on the basis of efficiency, power quality and cost.

- (2) To develop a cost effective DC offset control system for the grid connected PV system that would keep the level of DC injection into the AC network below the Australian Standard requirement;

- (3) To develop mathematical models that would help with design and implementation of the DC offset controller and other control loops used within the inverter system.

#### **1.3 Outline of Dissertation**

Chapter 2 of the dissertation is a review of existing inverter control and switching strategies. Their respective advantages and disadvantages, with specific reference to single phase photovoltaic systems, are discussed. This review, together with the literature review carried out in Chapter 3, has helped with the search for inverter control features that could potentially improve performance and cost. Chapter 3 also provides justification for the adopted methodology for this research project.

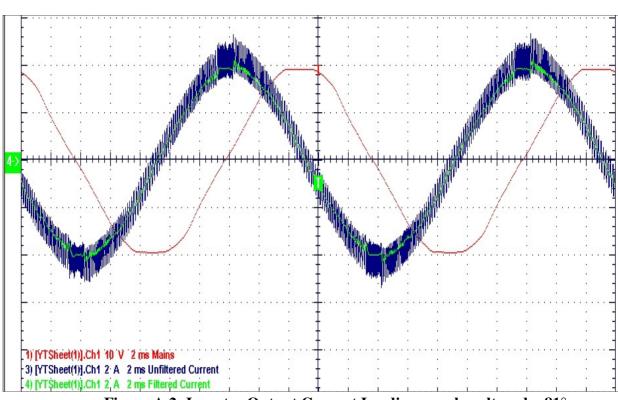

Chapter 4 is devoted to inverter switching. A detailed comparison of unipolar and bipolar switching is provided. Test results are presented which confirm that significant reduction in switching losses is possible if unipolar switching is adopted. However, there is unacceptable current distortion near the AC supply voltage zero crossing. It is demonstrated that appropriate combination of bipolar and unipolar switching techniques can achieve the switching loss reduction whilst avoiding the current distortion effects at the zero crossing of the AC supply voltage waveform.

Chapter 5 details the active power balance controller. The controller incorporates PV array maximum power tracking and DC bus voltage control.

Chapter 6 presents the details of three DC offset controllers. The first two are implemented using discrete analogue devices and are essentially PI controllers with two different types of sensing arrangements. The third one is digitally implemented. Mathematical models are developed and these are validated by test results. Chapter 6 also provides both theoretical and practical confirmation that there is no interaction between the DC offset control loop and either of the other two control loops.

Chapter 7 concludes the dissertation. It presents a summary of research achievements together with a discussion on their significance.

A single phase transformerless grid-connected photovoltaic system has been implemented and tested. Listed below are a number of its features which are considered to be novel and/or significant.

- (a) It incorporates a DC offset controller, which can be of analogue or digital design.

- (b) It can operate, as a four quadrant AC current controller, in a mixed unipolar/bipolar switching mode. It has been proven by experiment that the mixed switching method retains the efficiency advantage of unipolar switching without the typical current distortion that occurs near the AC supply voltage zero crossing.

- (c) Its control system requires modest speed and memory capabilities as typically found in small industrial programmable controllers.

- (d) Modulation of the current reference signal in response to insolation level is carried out using a digital potentiometer, thus avoiding analogue multiplication or the requirement for fast digital multiplication within the programmable controller.

The following publications are the research outcomes:

- (1) A.Ahfock and L.Bowtell, "DC Offset Elimination in a Transformerless Single Phase Grid-Connected Photovoltaic System", *Australasian Universities Power Engineering Conference*, 'AUPEC 06', Victoria University, Melbourne, 2006.

- (2) L.Bowtell and A.Ahfock, "Comparison Between Unipolar and Bipolar Single Phase Grid-Connected Inverters for PV Applications", *Australasian Universities Power Engineering Conference, 'AUPEC 07'*, Curtin University, WA, 2007.

- (3) L.Bowtell and A.Ahfock, "Direct Current Offset Controller for Transformerless single-Phase Photovoltaic Grid-connected Inverters", *IET Renewable Power and Generation*, vol. 4, iss. 5, pp. 428-437, 2010.

- (4) L.Bowtell and A.Ahfock, "Dynamic Analysis of a DC Offset Controller for Grid-Connected Inverters", *Australasian Universities Power Engineering Conference*, *'AUPEC10'*, Christchurch, NZ, 2010.

- (5) A.Ahfock and L.Bowtell, "Mixed Mode Switching of Single-phase Grid-connected Photovoltaic Inverters", *IET Renewable Power and Generation*, (submitted, Nov 2010).

## **Chapter 2**

### **Common Inverter Switching Control Strategies**

#### 2.1 Inverter Control Strategies

There are a large number of inverter configurations that could be used in grid connected photovoltaic systems. Different switching and control strategies could be adopted with each one of those configurations. It would not be possible to consider all possible combinations in a single document such as this one. Only those configurations with highest potential to achieve the aim of this research project are covered in detail. The purpose of this chapter is to provide background information that will assist with understanding of the reasons behind the short-listing of particular inverter configurations and control strategies.

#### 2.2 Voltage versus Current Controlled

A number of inverter control techniques can be used to inject power into the AC network. Two general possibilities are the voltage sourced voltage controlled inverter (VSVC) and the voltage sourced current controlled inverter (VSCC). The term 'voltage sourced' implies that the DC input to the inverter ( $v_c$  in figure 1.1) is essentially constant, at least within the time frame of a few inverter output cycles. Current sourced inverter systems are not normally used in photovoltaic applications and are not considered here.

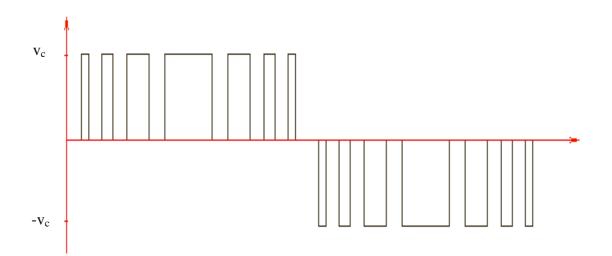

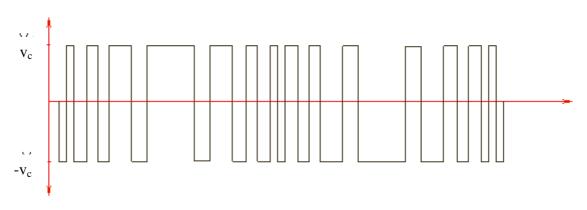

In the case of voltage control, the output voltage of the inverter ( $v_i$  in figure 1.1) is directly controlled. It is normally in the form of a sine-coded pulse width modulated (PWM) voltage, unipolar or bipolar. Assuming the power electronic switches in the inverter were

perfect, as shown in figure 2.1, unipolar voltage levels in the positive half cycle is  $(v_c)$  and 0 and in the negative half cycle they are  $(-v_c)$  and 0. In the bipolar case, as shown in figure 2.2, voltage levels in any of the half cycles, positive or negative, are ideally  $(v_c)$  and  $(-v_c)$ . In practice the number of pulses per inverter half cycle (or inverter switching frequency) is much higher than shown in figures 2.1 or 2.2.

In voltage control mode the rms value and phase of the inverter output voltage is directly controlled and the inverter output current will assume a magnitude, waveshape and phase that would depend on the AC network Thevenin voltage and the total series impedance that it experiences.

Figure 2.1: Output Voltage from Unipolar Switched Inverter

Figure 2.2: Output Voltage from Bipolar Switched Inverter

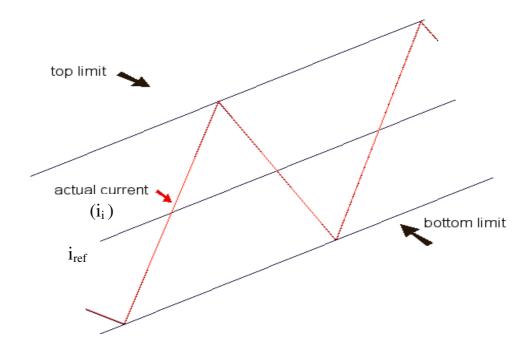

In the case of current control, the output current of the inverter ( $i_i$  in figure 1.1) is directly controlled. Typically a hysteretic controller is used. If the current falls outside a limit of the hysteretic band then the inverter power electronic devices are switched so that the current returns inside the band. A typical output current waveform from a current controlled inverter is shown in figure 2.3. The aim is to force the output current ( $i_i$ ) to follow the reference current ( $i_{ref}$ ).

Figure 2.3: Typical Unfiltered Output Current of a Current Controlled Inverter

In general voltage sourced voltage controlled (VSVC) inverters have been more popular in stand-alone systems as they tend to be less expensive in this application. However, meeting the Australian Standard[1] requirements on DC level injection with grid-connected transformerless voltage controlled inverters is inherently more difficult with VSVC inverters. With current controlled inverters synchronisation with the AC mains presents no difficulty and DC content is significantly easier to control. The decision was made, therefore, to consider only voltage sourced current controlled (VSCC) inverters for this project.

#### 2.3 Bipolar versus Unipolar Switching

The inverter shown in figure 2.4 is grid-connected, voltage-sourced, and currentcontrolled. It may be unipolar switched or bipolar switched.

Figure 2.4: Current Controlled Grid Connected Full Bridge Inverter

#### 2.3.1 Bipolar Switching

Consider the inverter in figure 2.4. If the aim is to achieve unity power factor, current reference signal  $(i_{ref})$  is arranged to be in phase with the supply voltage  $(v_s)$ . During the positive half cycle of the source voltage  $(v_s)$ , when current  $(i_i)$  falls below the bottom limit of the hysteretic band,  $T_{A+}$  and  $T_{B-}$  are switched on. As a result the current rises through

$T_{A+}$  and  $T_{B-}$ . If the current rises above the top limit of the hysteretic band,  $T_{A+}$  and  $T_{B-}$  are switched off and current  $(i_i)$  falls through  $D_{A-}$  and  $D_{B+}$ .

During the negative half cycle of the source voltage  $(v_s)$ , when current  $(i_i)$  goes above the top limit of the hysteretic band,  $T_{A_-}$  and  $T_{B_+}$  are switched on. As a result the current rises negatively through  $T_{A_-}$  and  $T_{B_+}$ . When the current goes below the bottom limit of the hysteretic band,  $T_{A_-}$  and  $T_{B_+}$  are switched off and current  $(i_i)$  falls towards zero through  $D_{A_+}$  and  $D_{B_-}$ .

In practice when a transistor pair is switched off (say  $T_{A+}$  and  $T_{B-}$ ), the next pair (say  $T_{A-}$  and  $T_{B+}$ ) is not switched on straight away. This is to ensure that the transistors being turned off are fully off before the next pair is turned on. The short time that is allowed to elapse between initiation of turn-off of one pair and initiation of turn-on of the next pair is called the blanking time. The blanking time used is of the order of one or two microseconds. Without a long enough blanking time, there is a risk of short-circuiting the inverter DC supply.

It appears from the previous paragraphs that  $T_{A}$  and  $T_{B+}$  are not needed during the positive half cycle of  $i_{ref}$  and similarly  $T_{A+}$  and  $T_{B-}$  are not needed during the negative half cycle. Ideally that would be the case at unity power factor. But generally speaking, unity power factor cannot be assumed and except for the duration of the blanking time there should always be one transistor pair switched on.

In other words, when one transistor pair is switched off the other pair should be switched on straight after expiry of the blanking time. Assuming unity power factor operation, reference current  $(i_{ref})$  is arranged to be in phase with AC supply voltage  $(v_s)$ . During the entire positive half cycle of the source voltage $(v_s)$ , insulated gate bipolar transistor  $T_{B+}$  is kept off and  $T_{B-}$  is kept on. Transistor  $T_{A+}$  is switched on when the inverter output current  $(i_i)$  goes below the bottom limit of the hysteretic band. This causes current  $(i_i)$  to rise while it flows through  $T_{A+}$  and  $T_{B-}$ . When current  $(i_i)$  goes above the upper limit of the band  $T_{A+}$  is switched off. This causes  $(i_i)$  to fall while it flows through  $D_{A-}$  and  $T_{B-}$ .

During the entire negative half cycle of the voltage  $(v_s)$ , transistor  $T_B$  is kept off and  $T_{B+}$  is kept on. Transistor  $T_{A-}$  is switched on when the inverter output current  $(i_i)$  goes above the top limit of the hysteretic band. This causes current  $(i_i)$  to rise negatively while it flows through  $T_{B+}$  and  $T_{A-}$ . When current  $(i_i)$  goes outside the lower limit of the band  $T_{A-}$  is switched off. This causes current  $(i_i)$  to fall towards zero while it flows through  $D_{A+}$  and  $T_{B+}$ .

Compared to the bipolar case switching frequency in the unipolar case becomes significantly low on approach of the zero crossing. The reason for this is that while the rise time of the inverter output current within the hysteretic band is proportional to  $(v_c - |v_s|)$ , the fall time is proportional to  $|v_s|$ . Thus as the zero crossing is approached fall time becomes longer and switching frequency is effectively lower. This, together with the necessary blanking time is responsible for zero-crossing distortion.

It appears from the previous paragraphs that  $T_{A}$  is unnecessary during the positive half cycle of  $i_{ref}$  and similarly  $T_{A+}$  is not needed during the negative half cycle. Ideally that would be the case at unity power factor. Generally speaking, unity power factor cannot be assumed and except for the duration of the blanking time there should always be one of either  $T_{A+}$  or  $T_{A-}$  switched on. That is when  $T_{A+}$  or  $T_{A-}$  is switched off then the complementry transistor  $T_{A-}$  or  $T_{A+}$  should be switched on straight after expiration of the blanking time.

Note that irrespective of the operating power factor, transistors  $T_{B+}$  and  $T_{B-}$  are switched only at the zero crossing of the AC supply voltage. The relatively low switching frequency of  $T_{B+}$  and  $T_{B-}$  is the reason behind the fact that a unipolar switched inverter suffers lower switching losses compared to the bipolar switched inverter.

#### 2.4 System Control Loops

The hysteretic controller described in section 2.2 forms the innermost control loop of the grid-connected PV system. Since there is no substantial storage between the output of the solar array and the output of the inverter, there is a need for control of power. The idea is to continuously adjust the rms value of the inverter output current( $I_i$ ) so that it is proportional to the power output from the solar array which is itself continuously changing. In other words, as insolation level rises or falls, the reference current ( $I_{ref}$ ) should automatically rise or fall in proportion so that power balance is preserved. It is the role of the voltage control loop to maintain balance between the solar array power output and power input into the AC network. This section covers the principles behind the voltage control loop in its own right. Whereas the voltage control loop aims for balance between power output from the array and power output of the inverter, the maximum power tracker is a immum power tracker aims to operate the solar array at a voltage level that would result in maximum extraction of power.

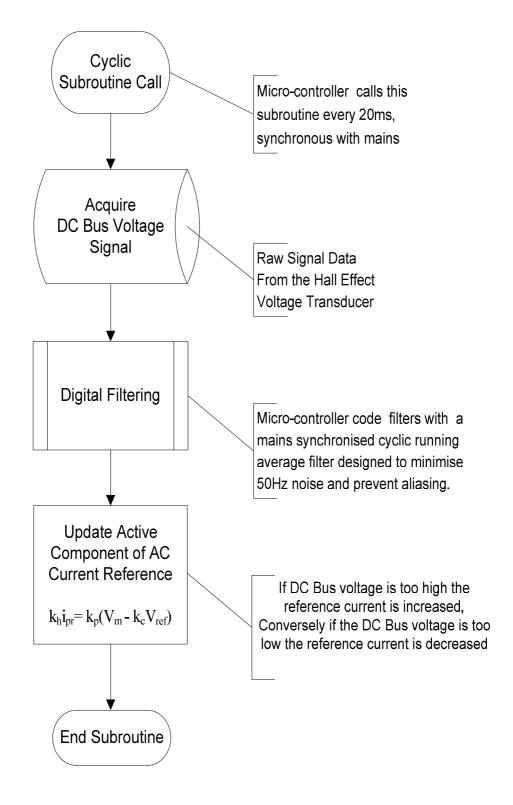

#### 2.4.1 DC Bus Voltage Control

As shown in figure 2.5, the DC bus voltage signal  $(k_c v_c)$  and the reference voltage  $(k_c.v_{ref})$  are inputs to the voltage controller. At steady state, the DC bus voltage signal  $(k_c v_c)$  will be practically equal to the DC bus reference voltage  $(k_c.v_{ref})$  and the controller output  $(k_h i_{pr})$  will be a constant. The output of the voltage controller is multiplied by the mains AC voltage signal  $(k_s.v_s)$  to produce the current reference signal  $(k_h.i_{ref})$ . The inverter output current signal  $(k_h i_i)$  and the current reference signal  $(k_h.i_{ref})$  are inputs to the hysteretic current controller which generates gate signals to switch appropriate inverter devices as described in section 2.3.

A rise in output power from the solar array tends to cause a rise in DC bus voltage( $v_c$ ) which in turn causes a rise in ( $k_h i_{pr}$ ). This causes  $I_{ref}$  (rms of  $i_{ref}$ ) to rise resulting in inverter output current  $I_i$  (rms of  $i_i$ ) rising because it tracks ( $i_{ref}$ ). The rise in current  $I_i$  restores power balance between the DC power output of the solar array and the AC power output of the inverter. Thus the aim of the voltage control loop is to maintain power balance by getting the DC bus voltage signal ( $k_c v_c$ ) to be practically equal to the reference ( $k_c v_{ref}$ ). The system shown in figure 2.5 is a single stage power balance controller unlike the system in [2] where a DC to DC converter stage is used. Some flexibility is lost in array configuration but this is offset by simplified control and removal of a switching stage and associated devices. Details of analysis and implementation of the voltage control loop are presented in chapter 5.

Figure 2.5: Inverter and Bus Voltage Control Loop

Although the grid connected PV system can operate with a constant bus voltage reference  $(v_{ref})$ , the consequence would be significantly reduced efficiency. The I-V curve of a solar array at a particular insolation level is shown in figure 2.6. If the array is operated well into the "current source" region, at operating point (*X*) for example, current is relatively high but voltage is low and consequently power output is low. On the other hand if the array is operated well into the "voltage source" region at operating point (*Z*) for example, voltage is relatively high but current is low and again power output is low. Note that in figure 2.6 power output is represented by the area of a rectangle. It is clear that there exists a point (*Y*) along the I-V curve somewhere between (*X*) and (*Z*) that corresponds to maximum power. The purpose of the maximum power tracker is to determine that point and to set the reference voltage ( $v_{ref}$ ) to correspond to that point. Assuming the maximum power tracker is operating correctly, the voltage controller would ensure that the array operates at the maximum power point.

Figure 2.6: PV Array Characteristic at Given Insolation and Temperature

The I-V characteristics of a solar array is a function of insolation level and temperature. This means that as insolation level or temperature changes the operating point changes. Referring to Figure 2.7, assume that the system is initially operating at optimum point  $(Z_I)$ . This implies that  $(v_{ref})$  is practically equal to  $(v_c)$ . However, if there is an increase in insolation level and the maximum power tracker is inactive, the operating point will shift to non-optimal point  $(Z_{no})$ . But the maximum power tracker is normally designed to continually check whether or not operation is optimal, and change the reference voltage accordingly. As shown in figure 2.7, as a result of the increased insolation level, the maximum power tracker will cause the operating point to shift from  $(Z_I)$  to  $(Z_2)$ .

Figure 2.7: The Need for Maximum Power Tracking

Figure 2.8: Grid Connected PV System with Maximum Power Tracker

Page 18

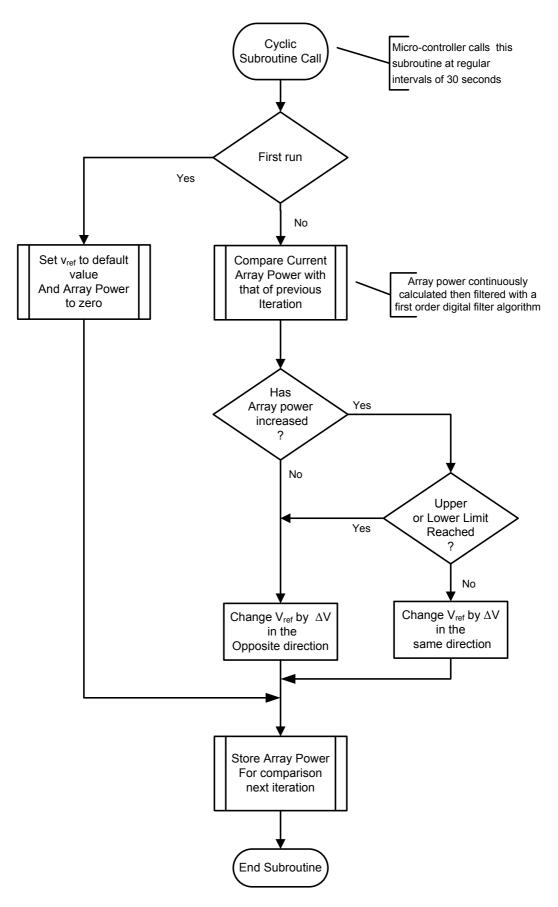

In essence, the maximum power tracking procedure involves the following steps:

- (a) Calculate and record array output power ( $v_c$ . $i_p$  in figure 2.8);

- (b) Adjust the voltage reference by  $\Delta v_{ref}$ , where  $\Delta v_{ref}$  is a small value;

- (c) Wait 30 seconds, allowing  $(v_c)$  to settle to its new value; (refer section 5.2)

- (d) Calculate and record the new value for array output power(averaged over the waiting time for step (c).

- (e) Calculate  $\Delta P$ , the change in array output power compared to the previous value.

- (f) Reverse the previous change in reference voltage if  $\Delta P \leq 0$  otherwise change the

voltage reference by  $\Delta v$  in the same direction as the previous change.

(g) Repeat steps (c) to (f).

Referring back to figure 2.7, the increase in insolation level will result in the maximum power tracker increasing the reference voltage from  $(v_1 + \Delta v)$  to  $(v_2 + \Delta v)$ . More specific details of the final MPPT implementation are given in chapter 5. More rapid changes can occur with cloud movement and this has been covered in previous work AUPEC93 where it was the focus of study, in the case of rapid transients the Bus voltage control loop will react accordingly.

#### 2.5 Potential for Cost and Performance Improvement

The review presented in this chapter, on inverter configurations and common switching and control strategies point to a number of questions which directly relate to potential cost and/or performance improvement.

These are:

- (a) Can the current controlled inverter work without a mains frequency isolating transformer and still operate within DC injection limits imposed by Australian and other standards? Would a DC offset controller have to be integrated in the inverter control system? Would that DC offset controller interfere with other inverter control loops? How would DC offset be sensed? How would the control parameters of the DC offset controller be arrived at?

- (b) Compared to bipolar operation, does unipolar operation, as a result of its lower number of switching operations per inverter cycle, have the advantage of lower power loss? How can the difference in power loss be measured in practice? Is there a power quality penalty if unipolar operation is adopted instead of bipolar operation?

The aim of the literature review presented in the next chapter is to identify previous research findings that could help address the above questions.

## **Chapter 3**

## **Literature Review and Project Plan**

This chapter covers a literature review and a summary of the adopted plan for the project. The literature review is focussed on the quality of power from grid-connected inverters, in particular the question of DC injection into the AC network by single phase photovoltaic systems and on the comparison between unipolar and bipolar switching methodologies.

### **3.1 Review of Literature**

#### 3.1.1 DC Offset Control

Ideally the output current of the inverter, forming part of a grid connected PV system, will be purely AC. However, in practice, unless special measures are taken, it will contain a small amount of DC. Injection of DC into the AC mains, if excessive, can lead to problems such as corrosion in underground equipment [3], transformer saturation and transformer magnetising current distortion [4] and malfunction of protective equipment [5]. Therefore guidelines and standards have been set up to regulate DC injection [6,7,8]. For example Australian Standard AS4777.2 [1] limits DC injection to 5mA or 0.5% of rated output whichever one is greater and, in the United Kingdom, ER G83/1 [8] imposes a limit of 20mA.

The simplest way to eliminate DC injection is to include a grid frequency transformer between the output of the inverter and the AC network. This has been the solution adopted in a number of commercial systems [6,9]. Inclusion of a grid frequency transformer implies major disadvantages such as added cost, mass, volume and power losses. Some commercial systems include a smaller higher frequency transformer or are transformerless. Salas [6], reports on measurements of DC currents from the AC output of commercial systems. Compared to the limits imposed by AS4777.2 [1] or by ER G83/1 [8], the measured DC currents were found to be very significant. Methods to solve the DC injection problem have been proposed by Masoud [3], Sharma [10] and Armstrong [11]. Masoud [3] and Sharma [10] both propose the use of a feedback loop to eliminate the DC offset in the inverter output. Masoud [3] suggests using a voltage sensor at the inverter output consisting of a differential amplifier and a low pass filter. Any DC detected at the output of the low pass filter is fed back to the controller which in turn operates the inverter in such a way as to reduce the DC offset. A simple mathematical model is suggested for the control system and it is assumed that the inverter is voltage controlled. However, experimental results are not reported.

Armstrong [11] proposes an automatic adjustment scheme to negate the effect of DC offset contributions from the Hall-effect current sensor in series with the DC input. Software is used to ensure that the current measurement made during freewheeling intervals is subtracted from all measured current values. This technique is however limited to unipolar switched inverters whose control enables the freewheeling intervals to be easily determined. Blewitt [12] considers using a large series electrolytic capacitor to block any DC component of current. This method requires an additional fast control loop and a slower capacitor offset voltage control loop while reporting a maximum of 5mA injected into the mains. Buticchi[13] also uses a sensor at the output of the inverter to detect DC voltage offset and a DSP to effect control. However it incurs additional losses and fails to meet the requirements of AS4777 [1].

Sharma [10] considers a current controlled inverter. Again a sensor is connected at the output of the inverter to detect the presence of any DC offset voltage. The sensor consists of an RC circuit and a 1:1 signal transformer. It is recognised that the DC signal is of the order of less than a few mV and needs to be extracted from a total signal of more than two hundred volts which is essentially the grid supply voltage. The RC circuit is connected in series with the secondary side of the 1:1 signal transformer. The series combination is connected across the inverter output. The primary side of the 1:1 signal transformer is connected across the AC supply. Thus, if it is assumed that the signal transformer is perfect and that the secondary voltage of the transformer opposes the AC supply voltage, only DC appears across the capacitor in the RC branch. The capacitor voltage is fed back to the controller which in turn adjusts the inverter current reference so that the DC offset is eliminated. No quantitative experimental results are reported, except for a statement that the DC offset controller has been found to operate correctly. A mathematical model of the controller is presented in a subsequent paper by Ahfock [14]. The mathematical model is experimentally validated and it is shown that the 1:1 transformer is effective only if its primary winding time constant is sufficiently low. In other words a relatively large core and a low winding resistance are necessary, making the DC offset sensor bulky and expensive.

In this project a simple two-stage RC filter will be used as DC offset sensor. Unlike the DC sensors in Masoud [3] and Sharma [10], where sensing is carried out across the AC supply terminals, the DC offset sensor in this project will be connected across the ripple filter inductor at the output of the inverter bridge as in Bowtell [15]. The disadvantage of sensing across the AC supply terminals is that the sensed DC offset could be due to sources other than the inverter. On the other hand the DC offset detected by the proposed sensor is guaranteed to be caused by the inverter being controlled. A design procedure will be

developed for the proposed DC offset controller. This will require investigating possible interactions between the DC offset control loop and other control loops within the system.

As pointed out in the previous section, the three other control loops are:

- (a) the Current Control Loop;

- (b) the DC Bus Voltage Control Loop;

- (c) and the Maximum Power Tracking Loop.

The design of those control loops is greatly simplified if, from a control point of view, they do not interact. A number of authors such as Raoufi [16] and Varjasi [17] have either implicitly or explicitly assumed that the DC bus voltage control loop does not interact with the other loops and they invariably use a mathematical model based on capacitor power balance to design the DC bus voltage controller. An objective of this research is to consider the dynamic response of each control loop in detail. The DC bus voltage control loop operates outside the current control loop. The voltage controller provides the reference signal for the current controller. The current loop operates much faster than the outer voltage loop. So they can be designed independently. When designing the voltage loop, the current loop may be assumed to be a pure gain. The current loop, on the other hand is designed under the assumption that the controlled current does not influence the reference current. In this project, as is normal practice, the voltage control loop and current control loop will be independently designed. However experimental verification will be carried out to confirm that there is no interaction between them.

The maximum power tracker, unlike the other loops, does not have a reference input. It is an extremum seeking loop. In single stage conversion systems, such as the one considered for this project and by others such as Varjasi [17] and Gonzales [19], the maximum power tracker provides the voltage reference for the voltage control loop. That voltage reference, once set by the maximum power tracker, is not immediately influenced by any other control loop. After setting the reference voltage to a new value, the maximum power tracker waits for the voltage controller to get the DC bus voltage to that value before operating again. Therefore the voltage control loop can be designed under the assumption that its operation does not influence its reference voltage.

There is very little that has been published on controlling the DC offset current at the output of a grid-connected PV system. There appears to be no work done so far on the question of possible interactions between a DC offset control loop and other control loops in the system. As part of this project, an attempt will be made to show that the design of a DC offset control loop can be made independent of the other control loops. In other words the aim will be to show that the DC offset control loop does not affect operations of the other loops and vice-versa.

#### **3.1.2 Output Current Harmonic Distortion**

Apart from a possible DC component, the output current of a grid-connected photovoltaic system contains harmonics. The harmonics can generally be classed as switching (or ripple) harmonics and low frequency harmonics. The ripple frequency, for systems in the kilowatt range, can be between a few kilohertz and tens of kilohertz. Low frequency harmonics are at integral multiples of the AC supply frequency.

Switching within the inverter can cause very fast charging and discharging of stray capacitances. The frequency spectra of the associated stray currents are in the megahertz range and can be a major cause of electromagnetic interference. Low frequency harmonics; ripple frequency harmonics; and electromagnetic interference will be considered in turn.

Grid connected PV systems have to meet the requirements of standards such as AS4777.2[1] which states that total harmonic distortion in the injected current should be less than 5% for harmonics up to the  $50^{\text{th}}$ . Many researchers have explored the question of such systems harmonic injection into the AC network, for example Kirawanich [20], and In common with other publications, all of these studies were based on [21-23]. measurements made on commercially available grid connected systems. Their results show that while the levels of low frequency harmonics are small they are still significant relative to the requirements of standards such as AS4777.2 [1]. Therefore there is a need to look carefully at causes of low frequency harmonics in grid-connected inverters with the aim of eliminating them or reducing their effects. There has been significant research activity in this area but the focus has been on voltage controlled systems. Oliva [25] lists possible causes of harmonics in voltage controlled converters as filter nonlinearities, deadtimes, device voltage drops and DC link voltage harmonics. Mohan [26] provides an explanation of relationship between dead-time and voltage harmonics. The use of deadtimes causes harmonics that manifest themselves as distortion at the current zero crossings. Kotsopoulos [27] suggests a simple mathematical model to quantify harmonic levels due associated with zero-crossing distortion. Oliveira [28] suggests a technique for reducing zero-crossing distortion due to dead-times. The proposed technique is, however, applicable to voltage controlled inverters. If the current reference is free of harmonics, the output current of current controlled inverters should be virtually free of low frequency harmonics. Nevertheless, Bowtell [29] has reported the presence of significant low frequency harmonic content at the output of current controlled inverters. There is very little in the published literature about the causes of low frequency distortion in current controlled inverters.

Possible reasons for low frequency distortion are:

(a) distortion in the current reference signal[30];

(b) distortion in the control signal generated by the voltage control circuit [31];

- (c) switching delay [32,33]

- (d) dead-time.

In the case of a unipolar switched inverter, there can be distortion near the negative going zero- crossing due to inability of the available AC supply voltage to bring the current down quickly enough so it can follow the reference. Similar distortion happens in switch-mode rectifiers at the positive going zero crossing of the rectifier input current Salmon [34]. It appears that bipolar switched current controlled inverters suffer significantly less zero crossing distortion. Lindgren [35], Ordonez [51] and Li [52] suggests using unipolar switching for most of the inverter cycles to exploit the potential switching loss reduction advantage and to use bipolar switching near the zero crossing to avoid zero crossing distortion.

An investigation into the causes of low frequency distortion, including zero crossing distortion, in current controlled inverters will be carried out as part of this project. A better understanding of those causes will make it easier to meet requirements specified by standards and help avoid the possibility of AC voltage distortion due to resonance effects.

Compared to low frequency harmonics, ripple frequency harmonics can be filtered out by relatively small and low cost components. Possibilities for ripple filtering are the L, LC and LCL filters. The LCL filter will be used in this project because it is the one that provides assurance against the occurrence of resonance. Bojrup [36] provides design guidelines for filter design. Although AS4777.2 [4], does not provide explicit guidelines on allowable ripple harmonic content, IEC 61000-3-2 [37], gives limits for harmonic currents up to the 40<sup>th</sup> and considers this inverter a class A device [37]. An important

reason for limiting injection of ripple frequency current is to avoid interference with systems that use power lines for communication. Practical guidelines for harmonic and voltage flicker are also found in [38] and [39]. The frequency range of ripple current from typical inverters overlaps with the frequency band used by power line communication systems. References [36,51,52] fail to adequately consider reasons for the existence of low frequency harmonics or ripple filter transients at the transition points between unipolar and bipolar operation.

Careful circuit layout is necessary if EMC requirements are to be achieved. It should also be taken into consideration that different circuit configurations results in drastically different levels of EMI emission depending on the level and the distribution of stray capacitive currents that result from inverter switching. Gonzalez [19] offers some theoretical insight into the charging and discharging of stray capacitances between the solar panels and earth, but no test results are provided. Jiang [40] reports on simulation carried out to study EMC of different inverter configurations. But the configurations are not relevant to those being investigated in this project. Gonzalez [19] argues that in the case where the ripple filter is made up of two identical inductors, one connected between terminal A of the inverter (see figure 2 in [19] ) and the neutral and the other between inverter terminal B and the active terminal, EMC performance is much better with bipolar operation than unipolar operation. As part of this project EMC performance will be investigated for the case where both inductors of the LCL filter are on neutral side. This particular case is of interest because this positioning of the inductors allows them to be readily used for DC offset current sensing.

#### 3.2 Project Plan

As a result of the above literature review and the assessment of inverter technologies reported in chapter 2, the following activities were planned and carried out:

- (a) Design, construction and testing of a single-phase transformerless, grid-connected, voltage sourced, current controlled inverter, that can operate both in bipolar and in unipolar modes: The main objective was comparison of power output quality and switching loss. The design incorporated several innovative features which are detailed in chapter 4. These included multi-mode switching to improve power quality and conversion efficiency. The inverter was designed to operate with a DC input voltage of up to 600V and to interface with the 240V, 50 Hz network.

- (b) Design and implementation of a software based power balance controller incorporating maximum power tracking and DC bus voltage control: A commercial programmable controller, the Siemens CPU222 [41], was used because it had the advantage of cost effectiveness, robustness and immunity to noise. A mathematical model was developed to help with the choice of control parameters.

- (c) Theoretical and practical investigation into DC offset controllers that use the inherent resistance of the current steering inductor (L<sub>i</sub> in figure 2.5) for DC offset current sensing: Both an analogue controller and a digital controller were planned. An integral control element was considered necessary since the design objective was to maintain zero steady state DC offset. Mathematical models were developed for both controllers. These models were used to help with controller design.

# **Chapter 4**

#### **Comparison of Bipolar and Unipolar Control**

#### 4.1: Introduction

This chapter is a detailed presentation on inverter operation. Three switching topologies are investigated. These are the unipolar mode, the bipolar mode and mixed-mode which is partly bipolar and partly unipolar. The main theoretical findings are supported by experimental results.

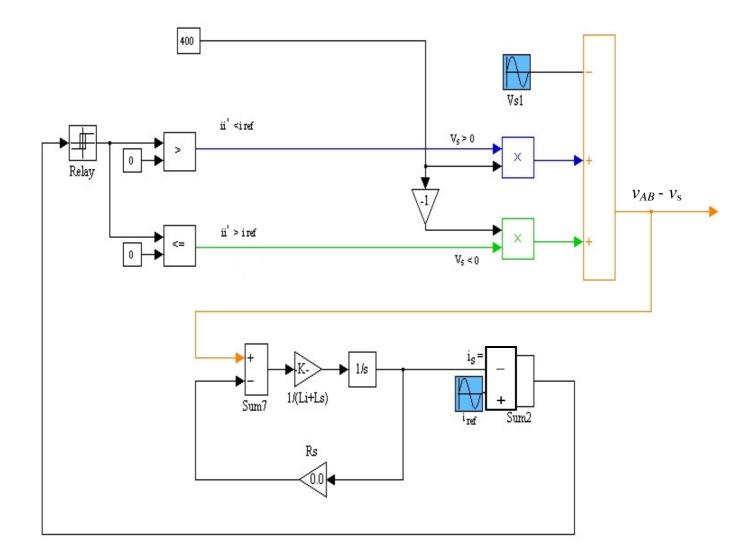

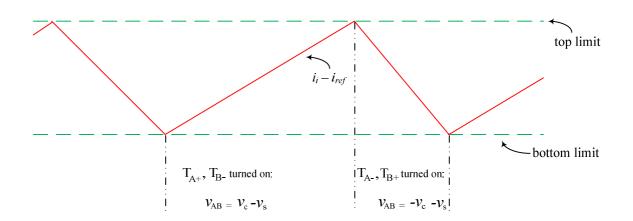

Section 4.2 deals with the bipolar switching mode which is conceptually the simplest. It is demonstrated in section 4.3 that the, potentially more energy efficient, unipolar switched inverter has the disadvantage of current distortion at the supply voltage zero crossings. In section 4.4 a hybrid mode switching technique is explored which is a combination of unipolar switching and bipolar switching. It is shown that with the mixed-mode switching scheme distortion at the zero-crossings is practically eliminated.

The effect of switching delay, which is ignored in section 4.4, is investigated in section 4.5. It is confirmed that switching delay, if significant enough will cause low frequency current distortion, even in the mixed-mode case. A solution to the problem is proposed and implemented. Section 4.6 provides practical evidence that unipolar switching and mixed-mode switching result in significantly lower switching losses when compared to a bipolar switching scheme.

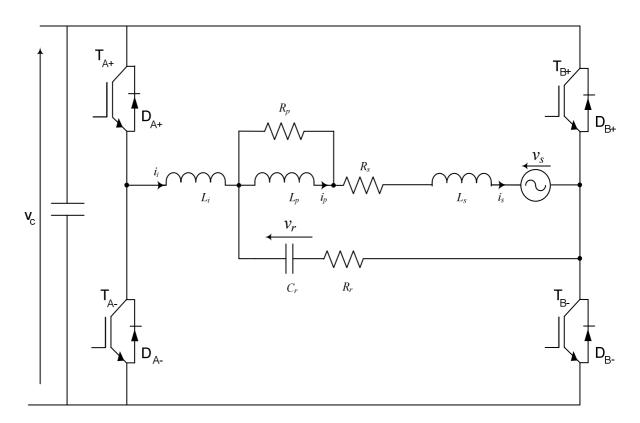

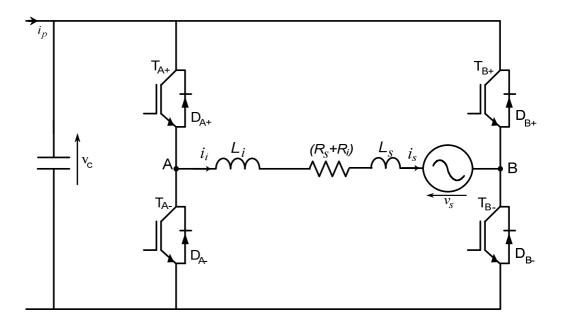

Figure 4.1: Inverter Components including LCL Filter

Figure 4.1 represents the inverter being considered in this chapter. The DC input voltage is fixed at 400V and the AC supply voltage is nominally 240V.  $R_s$  and  $L_s$  are the supply internal resistance and inductance respectively. Inductors  $L_i$ ,  $L_p$  and  $C_r$  form the LCL ripple filter. Resistors  $R_p$  and  $R_r$  are for filter damping.

## 4.2 Bipolar Switching without Ripple Filter

A Simulink® model of the ideal bipolar switched inverter is shown in figure 4.2.

The ripple filter, which will be considered later, has been left out here.

Figure 4.2: Simplified Bipolar Inverter Control Model

Figure 4.3: Hysteretic Control (no Ripple Filter)

Inverter switching is modelled by the relay block which operates in accordance with figure 4.3. The relay limits, +0.75A and -0.75A, represent the tolerance band of the current controller. When the current error  $(i_i - i_{ref})$ , reaches the bottom limit of the tolerance band, the output of the relay changes state. The voltage across the series combination made up of  $L_s$ ,  $R_s$  and  $L_i$  is equal to  $(v_c - v_s)$ . Conversely, when the current error  $(i_i - i_{ref})$  reaches the top limit of the tolerance band, the relay output changes state.

Figure 4.4: Simplified Bipolar Inverter Circuit

In this case the voltage across the series combination, as shown in figure 4.3, is equal to (- $v_c - v_s$ ). The values of  $L_s$  and  $R_s$  were estimated from fault level information at the point of

supply. A value of 10mH for  $L_i$  was considered reasonable because it allowed the maximum frequency requirement of 30kHz be met with a theoretical tolerance band of ±0.75A.  $R_i$  was measured as 0.36 $\Omega$ . Note that  $L_s$  and  $(R_i + R_s)$  in figure 4.4 are relatively small and could have been neglected.

**Figure 4.6:** Experimental Bipolar Operation  $(I_i = 2A)$

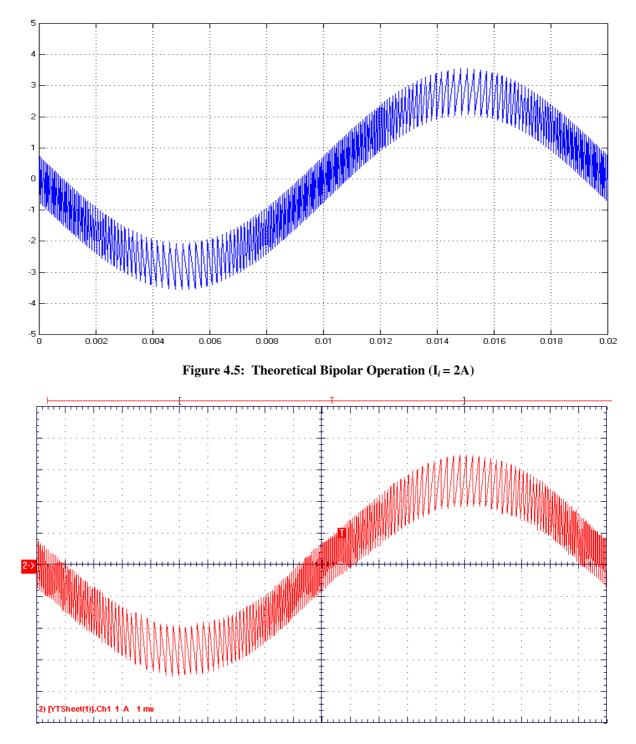

Figures 4.5 and 4.6 are respectively the theoretical prediction and test results for a reference current of 2.0A. There is very good correlation between them.

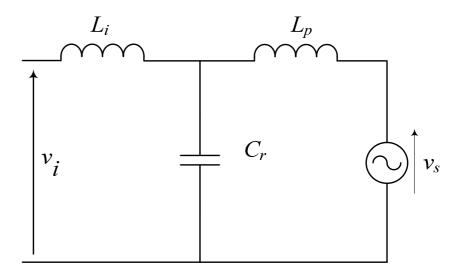

### 4.3 The Ripple Filter

Figure 4.7: LCL Filter Components

Injection of significant levels of ripple frequency current into the AC network is not acceptable. The LCL filter represented in figures 4.1 and 4.7 can be used to attenuate ripple frequency current injection. The rationale behind the choice of filter components is given below.

In summary, the design procedure for the filter consists of the following steps:

(a) Determine the value of  $L_i$  so that maximum switching frequency is not exceeded, the tolerance band is reasonable and the cost, mass and volume of the inductor is acceptable. A maximum switching frequency is imposed to limit switching losses. This helps with efficiency and reduces cooling requirements. For bipolar operation, the inverter switches at maximum frequency near the zero crossing of the supply voltage.

The relevant equation to determine  $L_i$  is:

$$L_i = V_c \Delta t / \Delta i$$

$$4.1$$

Page 35

where:

- $V_c$  = the DC bus voltage

- $\Delta t$  = half the minimum allowable switching period

- $\Delta i$  = size of the tolerance band

- (b) Calculate the lowest expected switching frequency of the inverter. For the bipolar inverter this will happen near the peak of the AC supply voltage. The relevant equations to estimate the minimum expected switching frequency is:

$$\Delta t_r = \frac{L_i \Delta i}{(V_c - \hat{V}_S)} \tag{4.2}$$

$$\Delta t_f = \frac{L_i \,\Delta i}{\left(V_c \,+\, \widehat{V}_S\right)} \tag{4.3}$$

$f_{min}$  = minimum switching frequency

$$= \frac{1}{(\ddot{A}t_r + \Delta t_f)} \tag{4.4}$$

For the prototype inverter constructed,  $f_{\min}$  was found to be 6.5kHz. This value is based on V<sub>c</sub>= 410V;  $\hat{V}_s = 339V$ ; L<sub>i</sub> = 10mH and  $\Delta i = 1A$  (c) Based on the specified ripple attenuation and neglecting resistive components and AC supply impedance, calculate the required value of  $L_pC_r$ . Assuming that the values of  $L_p$  and  $C_r$  are such that the inverter operates as intended, the ripple magnitude is constrained by the tolerance band and ripple attenuation is given by:

$$\frac{1}{k_r} = \frac{-1}{1 - \omega^2 \mathrm{L_p}\mathrm{C_r}} \tag{4.5}$$

where  $\omega$  = ripple frequency

and  $k_r$  = specified attenuation at the lowest inverter switching frequency

From equation 4.5 we have:

$$L_p C_r = (k_r + 1) / \omega^2$$

4.6

For the prototype inverter that was constructed  $L_p C_r$  was calculated as  $4 \times 10^{-9} \text{S}^{-2}$

for an attenuation factor of 5.6 at  $\omega_{min}$ .

(d) Select values for  $L_p$  and  $C_r$  based on the value of  $L_pC_r$  determined in step (c). Choosing a small value for  $L_p$  has the advantage of low cost. The impedance presented by the parallel LC circuit to the ripple current from the inverter is given by:

$$Z_p = j\omega L_p / k_r \tag{4.7}$$

- (e) Equation 4.7 implies that using a small value for  $L_p$  makes  $Z_p$  small. This has the advantage of keeping the inverter switching as intended. In other words the  $L_pC_r$  parallel contribution does not have a significant or detrimental effect on inverter switching. However, for a given value of  $L_pC_r$  if  $L_p$  is made too small then the required value of  $C_r$  can become excessive. A large value of  $C_r$  demands a leading component of power frequency current which should normally be limited.

- (f) Taking the above two opposing factors into consideration  $L_p$  and  $C_r$  were respectively chosen to be 2mH and 2µF. With those values  $Z_p$  is equal to 12 $\Omega$  at the lower limit of the inverter switching frequency. This value is thirty times lower than  $L_i\omega$  at the same frequency. Since  $Z_p$  appears in series with  $L_i\omega$ , it is expected that  $Z_p$  will not influence the inverter current flowing through  $L_i$ . The power frequency leading current due to  $C_r$ is 0.14A which is considered acceptable.

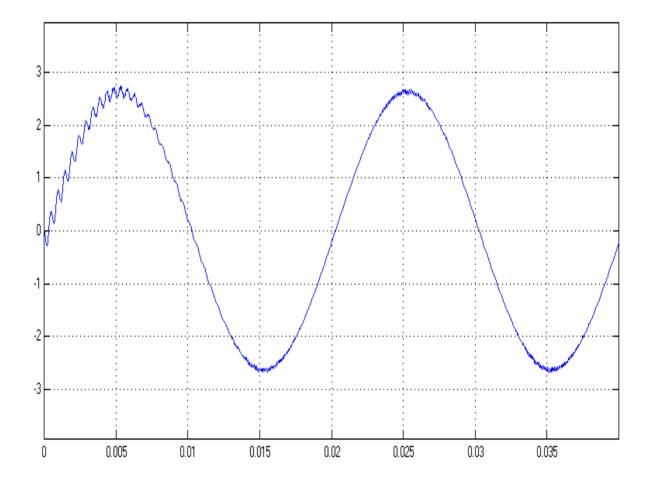

The values of filter capacitance and inductance arrived at in the previous section were based on steady state analysis. In practice the filter will not be purely in the steady state. From time to time it will be subject to transients. Examples are transients at inverter turn-on and transients due to sudden changes in the reference current magnitude. Without damping, as shown in figure 4.8, an oscillatory component of current gets injected into the AC network after such transient events. The frequency of that current component is approximately equal to:  $1/\sqrt{L_pC_r}$ .

Figure 4.8: Undamped Filtered Waveform (simulated)

Three possibilities were explored for the addition of damping to the ripple filter. These are illustrated in figure 4.9. A damping resistor will have the following effects:

- a. Natural filter oscillations will decay relatively quickly

- b. Filter power loss will increase

- c. The ripple attenuation will be adversely affected.

**Figure 4.9: Filter Damping Options**

The choice of filter resistance is based on balancing the desirable damping effect against the undesirable increase in filter losses and decrease in ripple attenuation. Equations 4.8 to 4.13 have been derived to assist with the selection of the damping resistance.

The three filter damping configurations shown in figure 4.9 respectively have the following characteristic equations:

$$sL_i[s^2 + s/(R_f C_r) + (1/L_p + 1/L_i)/C_r]$$

4.8

$$sL_i[s^2 + s(1 + L_p / L_i)(R_r / L_p) + (1 + L_p / L_i) / (L_p C_r)]$$

$$4.9$$

$$sL_i[s^2 + s/(R_p C_r) + (1/L_p + 1/L_i)/C_r]$$

$$4.10$$

The decay time constants from the above expressions are respectively:

$$\tau = R_f C_r \tag{4.11}$$

$$\tau = L_p / [R_r (1 + L_p / L_i)]$$

4.12

$$\tau = R_p C_r \tag{4.13}$$

For each of the damping options, damping resistance power loss is respectively given by:

(a) Power loss

$$\approx V_s^2 / R_f$$

4.14

(b) Power loss

$$\approx (V_s C_r \omega_s)^2 R_r + I_{tol}^2 R_r$$

4.15

(c) Power loss

$$\approx (I_i)^2 \omega_s^2 L_p^2 R_p / (\omega_s^2 L_p^2 + R_p^2)$$

4.16

The previous three equations are based on the following reasonable assumptions:

- i. The voltage across the capacitor is practically equal to the AC supply voltage.

- ii. Practically all the ripple current flows through the capacitive branch of the filter.

- iii. For the case of  $R_p$  (equation 4.16), power loss is a function of inverter output current.

Table 4.1 shows the respective power loss for a range of resistance values used with each of the three methods described above.

| Power<br>loss  | 0.1W   | 0.2W   | <b>0.4W</b> | 2.5W | 5W   | 7.5W  | 10W   |

|----------------|--------|--------|-------------|------|------|-------|-------|

| R <sub>f</sub> | 580k Ω | 270k Ω | 150k Ω      | 22kΩ | 12kΩ | 8.2kΩ | 5.6kΩ |

| R <sub>r</sub> | 0.18 Ω | 0.33 Ω | 0.68 Ω      | 4.4Ω | 8.6Ω | 12.8Ω | 17.1Ω |

| R <sub>p</sub> | 100 Ω  | 47 Ω   | 22Ω         |      |      |       |       |

$\textbf{Table: 4.1 Filter Power Loss Comparison} \quad (L_p = 2mH; V_s = 240V; C_r = 2\mu F, I_i = 4.5A; I_{tol} = 0.75A)$